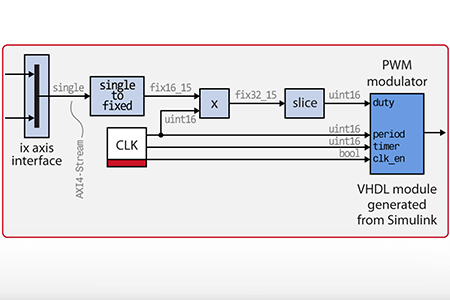

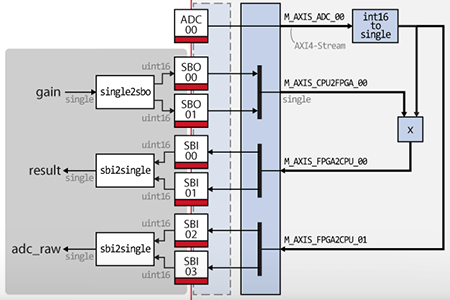

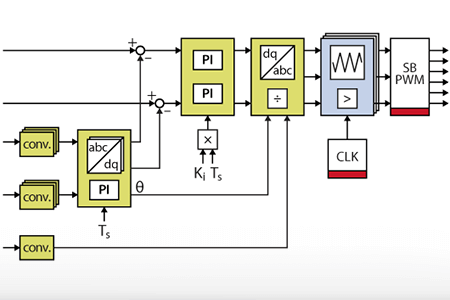

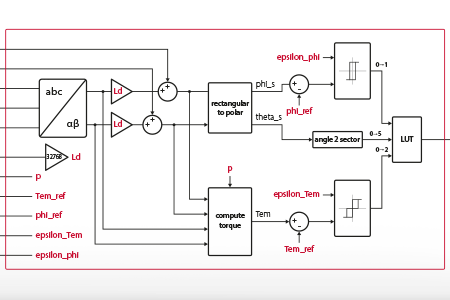

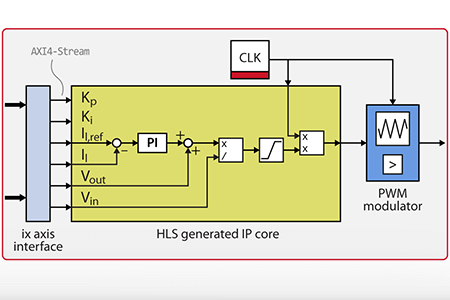

Custom PWM modulator implementation in FPGA

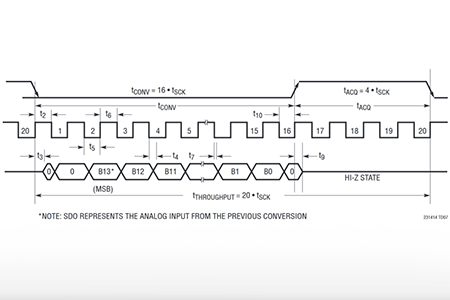

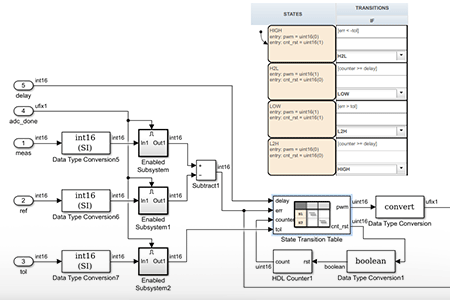

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents how to implement a custom PWM modulator in the Xilinx FPGA of the imperix controller (B-Box RCP or B-Board PRO). The presented modulator uses FPGA pulse-width modulation with a triangular…