## Getting started with FPGA control development

PN159 | Posted on June 2, 2021 | Updated on May 7, 2025

Benoît STEINMANN Software Team Leader imperix • in

#### **Table of Contents**

- Presentation of the FPGA control starter template

- Creating the FPGA control starter template

- Downloading the required sources

- Starting a new imperix sandbox project

- Adding the AXI4-Stream interface

- <u>Using the SBIO\_BUS</u>

- SBIO modules

- SBIO interconnect

- How the AXI4-Stream interface operates

- <u>Retrieving analog measurement with the M\_AXIS\_ADC interfaces</u>

- Exchanging data using M\_AXIS\_CPU2FPGA and S\_AXIS\_FPGA2CPU

- Getting the sample time Ts

- <u>Using reset signals</u>

- <u>Step-by-step "hello world" example</u>

- o <u>CPU-side implementation</u>

- FPGA-side implementation

- Loading the bitstream into the imperix controller

- Experimental validation

- Going further

- Testing M\_AXIS\_Ts

- Using the USR pins

- Additional tutorials

This note explains how to get started with the implementation of power converter control algorithms in the FPGA of <u>imperix power electronic controllers</u>. The benefit of offloading all or parts of the computations from the CPU to the FPGA is that it often results in much faster closed-loop control systems.

First, the **FPGA control starter template** is presented and a tutorial on how to create this template is provided. Then, the reader will learn how to **retrieve ADC results** from the FPGA as well as to **exchange data with the CPU**. The page ends with a simple hello-world example illustrating all the keys steps of FPGA control implementation.

This page is the first of a 3-part tutorial explaining step-by-step how to implement the closed-loop control of a buck converter in FPGA without using VHDL or Verilog. The second note explains how to generate a <u>PWM modulator in FPGA</u> using the Simulink blockset Xilinx System Generator or MATLAB HDL Coder. The last note shows how to create the <u>PI-based current control using high-level synthesis</u> with Xilinx Model Composer (Simulink blockset) or Xilinx Vitis HLS (C++).

To find all FPGA-related notes, please visit FPGA development homepage.

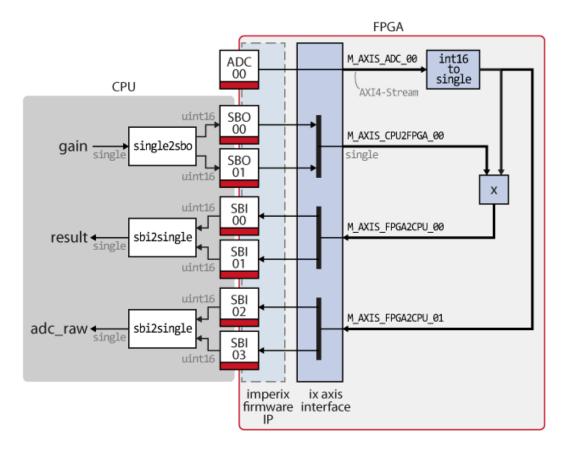

#### Presentation of the FPGA control starter template

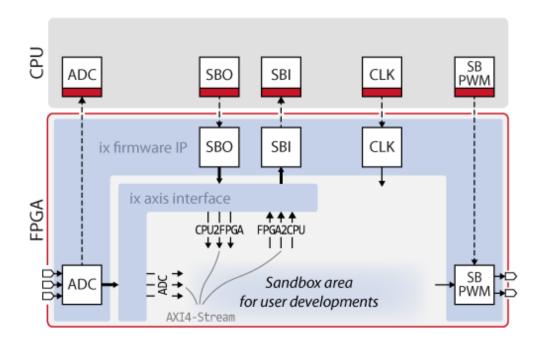

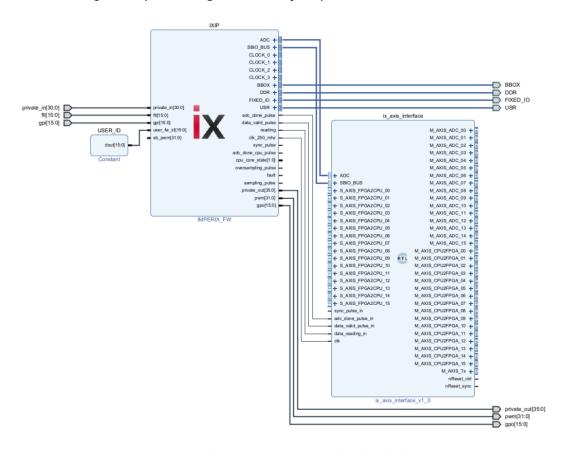

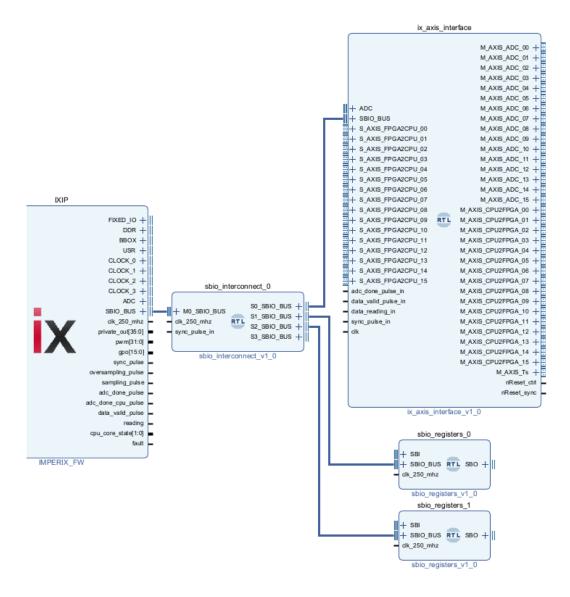

The FPGA control starter template allows for easy integration of custom FPGA-based control algorithms in the **sandbox** area of the <u>B-Box RCP</u> or the <u>B-Board PRO</u>. As shown in the image below, it consists of:

- the obfuscated "imperix firmware IP" which contains the FPGA logic required to operate imperix controllers (documented in PN116), and

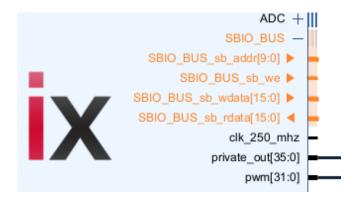

- the "ix axis interface" module which provides easy-to-use AXI4-Stream interfaces to exchange data with the user logic.

The provided AXI4-Stream interface module connects to the data interfaces and timing signals of the imperix firmware IP, interprets these signals, and converts them into much more user-friendly AXI4-Stream (AXIS) interfaces (ADC, CPU2FPGA and FPGA2CPU). The AXI4-Stream protocol is a widely used standard to interconnect

components that exchange data. This means that the provided template can directly be connected to a wide range of <u>Xilinx-provided IPs</u> or to user-made algorithms developed using High-Level Synthesis (HLS) design tools such as <u>Vitis HLS</u> (C++) or <u>Model Composer</u> (Simulink).

This AXI4-Stream interface module is written in VHDL. It is provided as a starting point and will meet the need of most applications. However, if required, it can be edited by the user to add extra input/outputs, rename them, change their data sizes, etc.

# **Creating the FPGA control starter template**

This tutorial requires Xilinx Vivado which is available at no-cost.

The <u>Vivado Design Suite installation</u> guide explains how to download and install Xilinx Vivado for free.

## **Downloading the required sources**

All the required sources are packed into the **FPGA\_Sandbox\_template** archive which can be downloaded from the <u>Download and update imperix IP</u> page.

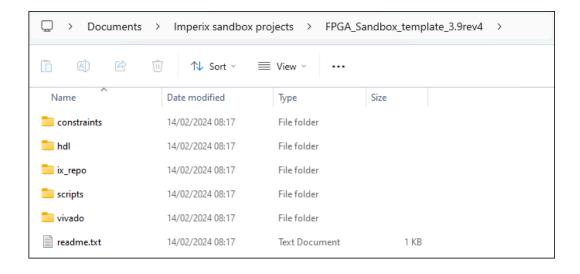

Since version 3.9, the template file structure is the following

- constraints

- o sandbox\_pins\_\*.xdc: top-level ports to a physical package pin assignation

- hdl

- AXIS\_interface.vhd: AXI4-Stream interface module, presented on the next chapter

- user\_cb\_pwm.vhd: simple carrier-based modulator, described in TN141

- **ix\_repo**: Vivado IP Catalog repository. Contains the imperix firmware IP and its interfaces.

- scripts:

- o create\_project.bat: launch Vivado and call create\_project.tcl

- create\_project.tcl: contains the TCL commands that create and configure the sandbox Vivado project

- vivado: contains the Vivado projects generated by the create\_project script

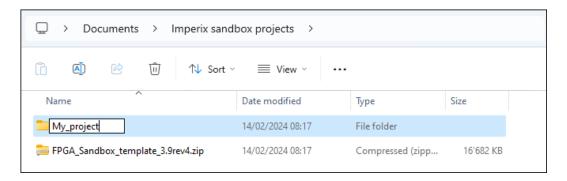

## Starting a new imperix sandbox project

- 1. Download FPGA\_Sandbox\_template\_\*.zip

- 2. Unzip it and save the content somewhere on the PC

- 3. Rename the folder to something more explicit

- 4. Open scripts/create\_project.bat using a text editor

- 5. Set the vivado\_path variable to match the Vivado version installed on the PC

6. Double click on **scripts/create\_project.bat**Windows Defender SmartScreen may display a warning pop-up. Simply click *More info* then *Run anyway*.

7. Enter a project name and click enter

```

C:\Windows\system32\cmd.e: \times + \times - \to \times \times \times \text{Please enter a project name.}

Project names must start with a letter (A-Z, a-z) and must contain only alphanumeric characters (A-Z, a-z, 0-9) and underscores (_)

Project name: my_project

```

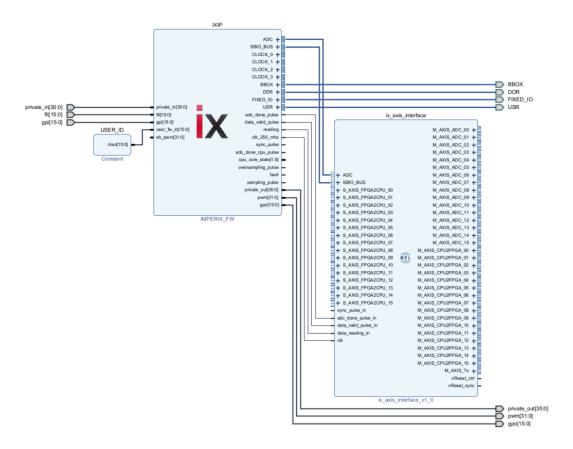

The Vivado sandbox project will be created and configured, its block design is shown below.

imperix sandbox template Vivado block design

If, for some reason, the script is not working properly then the Vivado project can be created manually by following the procedure below:

#### Manually creating Vivado imperix sandbox project

- 1. Open Vivado.

- 2. Click Create Project.

- 3. Chose a name and a location.

- 4. Select project type **RTL Project** and check the box **Do not specify sources at this time**.

- 5. Select the part named xc7z030fbg676-3.

- 6. Hit Finish. The project should open.

- 7. Go to the **IP Catalog**, right-click on **Vivado Repository**, hit **Add repository...**Select <my\_project>/ix\_repo/

The *IMPERIX\_FW* IP, *clock\_gen*, and *user\_regs* interfaces should be found. Press **OK**.

- 8. Click on Create block design, name it "top" and click OK.

- 9. Open the freshly created block design, do a right-click in a blank area of the design, select **Add IP...** and search for "IMPERIX\_FW" and hit ENTER.

- 10. Keep the [Ctrl] key pressed and select the IP pins flt, gpi, private\_in, DDR, FIXED\_IO, BBOS, USR, gpo, pwm and private\_out. Hit [Ctrl+T] to create top-level ports.

- 11. By default Vivado adds "\_0" after each port name. Remove the "\_0" from every port. For that, click on each port and change the **name** property in the **Block Pin Properties** block (appearing on the left of the diagram by default). For instance, change "flt 0[15:0]" to "flt[15:0]".

- 12. The user\_fw\_id input may be used to identify the firmware version. We recommend instantiating a *Constant* IP (Right-click, **Add IP...**, search for *Constant*) to give an identification number to the design. To change the constant width, double-click on the **Constant** block and set the **Const Width** to 16.

- 13. Go to the Sources tab, right-click on the block design file (top.bd) and select Create HDL Wrapper...

In the dialog box choose Let Vivado manage wrapper and auto-update and hit OK.

- 14. Right-click on the **Design Sources** folder

Choose Add Sources...

Check Add or create constraints

Click on **Add Files**

Select <my\_project>/sandbox\_pins.xdc

Uncheck Copy constraints files into project

Hit Finish

From this point the project is synthesizable.

#### Adding the AXI4-Stream interface

Adding the *AXI4-Stream interface* is optional. It is useful if the FPGA control design uses AXI4-Stream interfaces.

1. Right-click on **Design Sources**

Choose Add Sources....

Check Add or create design sources.

Press Add Files. Go to your repository and select <my\_project>/AXIS\_interface.vhd.

- We recommend unchecking "Copy sources into project" and working directly from the files in the folder <my\_project>/hdl/ so the sources can be shared across multiple projects. Press **Finish** and wait for the update to finish.

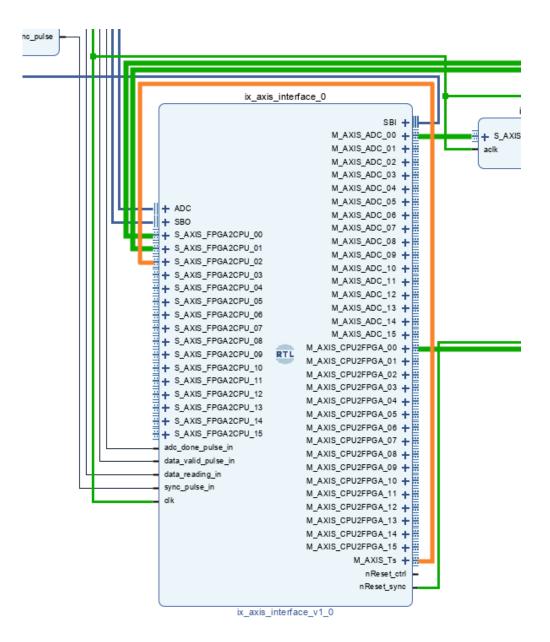

- 3. Right-click somewhere in the block design and choose **Add module...** and select the *ix\_axis\_interface* module. Alternatively, the file listed in the *Design Sources* can be drag and dropped it on the block diagram.

- 4. Connect the pins as follows (to get a clear layout, change "Default View" to "No Loops" in the top bar of the Diagram block, then right-click somewhere in the block design and press **Regenerate Layout**)

imperix sandbox template Vivado block design

# Using the SBIO\_BUS

The **SBIO\_BUS** (**S**and**B**ox **IO** bus) is a 16-bit memory-mapped bus allowing the CPU to addressing up to 1024 register in the FPGA.

#### **SBIO** modules

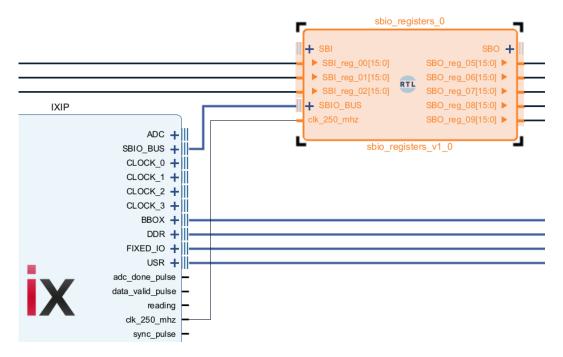

Two **SBIO modules** are provided in the template:

- the AXI4-Stream interface (AXIS\_interface.vhd) which is described in the next section,

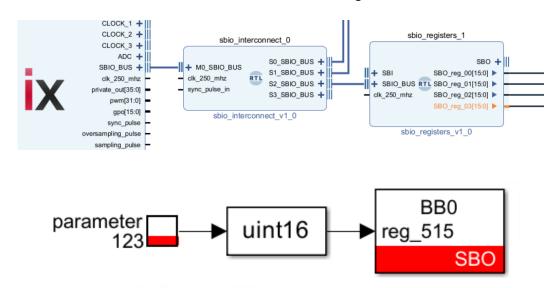

- the **SBIO** registers (sbio\_registers.vhd) shown below, which provides 16-bit registers that can easily be connected to user logic.

The user can read and write from this bus using the <u>SBO</u> and <u>SBI</u> blocks as shown below. During execution, SBIs are read before each CPU task executions and SBOs written at the end of each CPU task execution.

#### **SBIO** interconnect

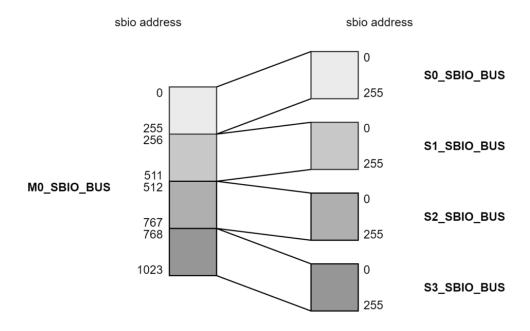

The **SBIO** interconnect increases the number of SBIO\_BUS interfaces, allowing to connect multiple SBIO modules as illustrated below.

sbio\_interconnect

The address mapping of the SBIO interconnect is shown below, it divides the SBIO addressable range in 4 smaller areas.

sbio\_interconnect memory mapping

As an example, to write to **SBO\_reg\_03** of an sbio\_registers block connected to **S2\_SBIO\_BUS**, The user has to use an SBO block to register number 512+3=**515**.

## **How the AXI4-Stream interface operates**

This section focuses on the *AXI-Stream interface* module (ix\_axis\_interface). For further information on the *imperix firmware* IP (IMPERIX\_FW) please refer to the <u>imperix firmware IP product guide</u>.

If required, AXIS\_interface.vhd can easily be edited to improve the readability, by renaming the interfaces and removing the unused ones for instance. In this example, the interface is kept as it is.

# Retrieving analog measurement with the M\_AXIS\_ADC interfaces

The *Master AXI4-Stream* interfaces **M\_AXIS\_ADC\_00** to **M\_AXIS\_ADC\_15** correspond to the 16 analog inputs of the imperix device.

They return the raw **16-bit signed integer** result from the ADC each time conversion results are available. Consequently, users should manually perform the data-type conversion and apply correct gains in their FPGA projects, to transform the acquired value in its physical unit. To learn how to compute this gain, please refer to the last section of the <u>ADC</u> page.

The ADC sampling frequency can only be configured using the <u>CONFIG</u> block. ADC acquisition can not be triggered from within the FPGA.

# Exchanging data using M\_AXIS\_CPU2FPGA and S\_AXIS\_FPGA2CPU

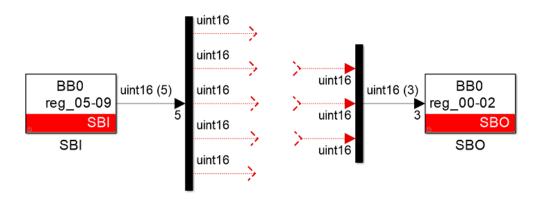

The *Master AXI4-Stream* interfaces **M\_AXIS\_CPU2FPGA** and the *Slave AXI4-Stream* interfaces **S\_AXIS\_FPGA2CPU** serve to exchange **32-bit** data between the CPU code and the FPGA.

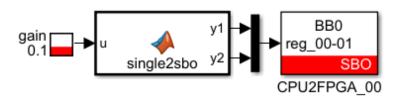

To read/write values on the FPGA2CPU/CPU2FPGA ports, the user can download the Simulink model from the step-by-step hello world section below and re-use the following blocks

write a float value from the CPU to the FPGA

The provided template uses the following mapping between the 16-bit SBI/SBO registers and the 32-bit AXI4-Stream interfaces:

| bit number  | 31 16  | 15 0   |

|-------------|--------|--------|

| CPU2FPGA_00 | SBO_01 | SBO_00 |

| CPU2FPGA_01 | SBO_03 | SBO_02 |

| CPU2FPGA_02 | SBO_05 | SBO_04 |

| CPU2FPGA_03 | SBO_07 | SBO_06 |

| CPU2FPGA_04 | SBO_09 | SBO_08 |

| CPU2FPGA_05 | SBO_11 | SBO_10 |

| CPU2FPGA_06 | SBO_13 | SBO_12 |

| CPU2FPGA_07 | SBO_15 | SBO_14 |

| CPU2FPGA_08 | SBO_17 | SBO_16 |

| CPU2FPGA_09 | SBO_19 | SBO_18 |

| CPU2FPGA_10 | SBO_21 | SBO_20 |

| CPU2FPGA_11 | SBO_23 | SBO_22 |

| CPU2FPGA_12 | SBO_25 | SBO_24 |

| CPU2FPGA_13 | SBO_27 | SBO_26 |

| CPU2FPGA_14 | SBO_29 | SBO_28 |

| CPU2FPGA_15 | SBO_31 | SBO_30 |

| bit number  | 31 16  | 15 0   |

|-------------|--------|--------|

| FPGA2CPU_00 | SBI_01 | SBI_00 |

| FPGA2CPU_01 | SBI_03 | SBI_02 |

| FPGA2CPU_02 | SBI_05 | SBI_04 |

| FPGA2CPU_03 | SBI_07 | SBI_06 |

| FPGA2CPU_04 | SBI_09 | SBI_08 |

| FPGA2CPU_05 | SBI_11 | SBI_10 |

| FPGA2CPU_06 | SBI_13 | SBI_12 |

| FPGA2CPU_07 | SBI_15 | SBI_14 |

| FPGA2CPU_08 | SBI_17 | SBI_16 |

| FPGA2CPU_09 | SBI_19 | SBI_18 |

| FPGA2CPU_10 | SBI_21 | SBI_20 |

| FPGA2CPU_11 | SBI_23 | SBI_22 |

| FPGA2CPU_12 | SBI_25 | SBI_24 |

| FPGA2CPU_13 | SBI_27 | SBI_26 |

| FPGA2CPU_14 | SBI_29 | SBI_28 |

| FPGA2CPU_15 | SBI_31 | SBI_30 |

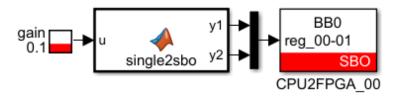

If the user chooses to write a single-precision floating-point data on the AXI4-Stream interfaces **M\_AXIS\_CPU2FPGA\_00**, then he has to:

- 1. use a <u>MATLAB Function block</u> to transform a *single* value into two *uint16* values (see code below)

- 2. and then use the <u>SBO</u> block to send these two *uint16* values to SBO\_reg\_00 and SBO\_reg\_01 (CPU2FPGA\_00).

```

function [y1,y2] = single2sbo(u)

temp = typecast(single(u), 'uint16');

y1 = temp(1);

y2 = temp(2);Code language: Matlab (matlab)

```

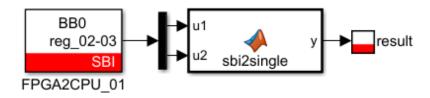

And if he wishes to read a result from the FPGA to the CPU (still in single-precision floating-point format) using **S\_AXIS\_FPGA2\_CPU\_01**, then he has to:

- 1. use the <u>SBI</u> block to retrieve the two *uint16* values from SB0\_reg\_02 and SB0\_reg\_03 (FPGA2CPU\_01)

- 2. and then use a MATLAB Function block to transform these two *uint16* values into a *single* value (see code below).

```

function y = sbi2single(u1,u2)

y = single(0); % fix simulink bug: force compiled size of output

y = typecast([uint16(u1) uint16(u2)], 'single');Code language: Matlab (matlab)

```

# **Getting the sample time Ts**

The **M\_AXIS\_Ts** interface provides the sample period in nanoseconds in a 32-bit unsigned integer format. This signal may be used, for instance, by the integrators of PI controllers. This value is measured by counting the time difference between two *adc\_done\_pulse*.

#### **Using reset signals**

The AXI4-Stream module also provides two reset signals:

- **nReset\_sync**: this reset signal is activated each time the user code is loaded through Cockpit. It can be used as a standard reset signal.

- **nReset\_ctrl**: this reset is triggered from the CPU through *SBO\_reg\_63* using a <u>core state</u> block. Its intended use is, for instance, to reset the PI controller integrator when the converter is not operating (when the PWM outputs are disabled).

Both signals are active-low and activated for 4 periods of c1k\_250\_mhz.

# Step-by-step "hello world" example

This simple "hello world" example serves to showcase the complete FPGA development workflow on Vivado.

As illustrated on the image below, it does the following:

- 1. From the CPU, a *gain* value (single-precision) is transferred to the FPGA using the **CPU2FPGA\_00** interface (SBO\_00 and SBO\_01).

- 2. In the FPGA, the data coming from the **ADC\_00** interface is converted into a *single* value.

- 3. The ADC value is then multiplied by the gain.

- 4. Finally, the multiplication result is sent back to the CPU through **FPGA2CPU\_00**.

- 5. The raw value of the ADC is also sent to the CPU using FPGA2CPU\_01.

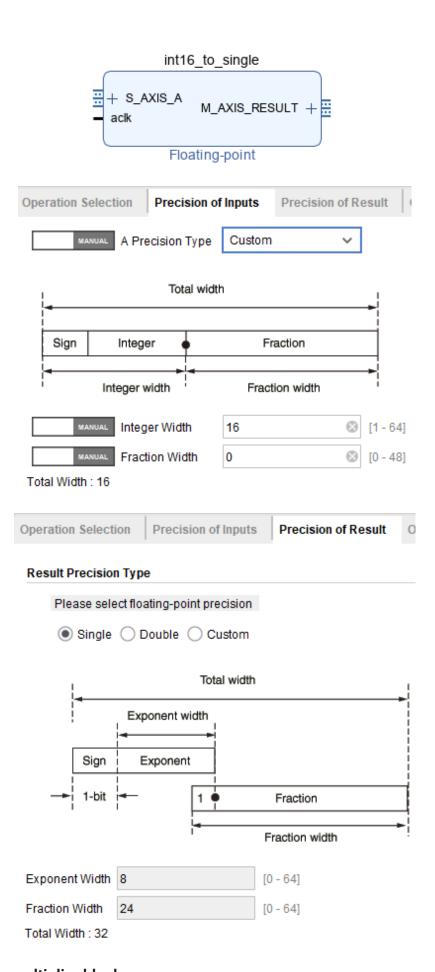

The FPGA logic will be implemented using exclusively readily available Xilinx Vivado IP, namely:

- **Floating-point IP** configured for *Fixed-to-float* operation to convert an int16 to a single-precision floating-point value.

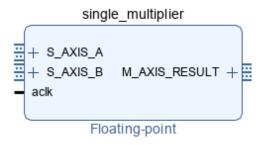

- **Floating-point IP** configured for the *Multiply* operation to multiply two single-precision floating-point values.

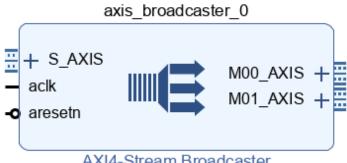

- **AXI4-Stream Broadcast IP** to duplicate the output of the *int16 to single* block.

Other useful Xilinx Vivado IPs are listed in the <u>AXI4-Stream IPs from Xilinx</u> page. The user can also implement his own IP blocks, either using directly VHDL or Verilog, or high-level design tools such as <u>Vitis HLS</u> (C++) or <u>Model Composer</u> (Simulink).

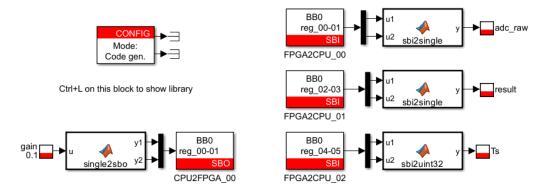

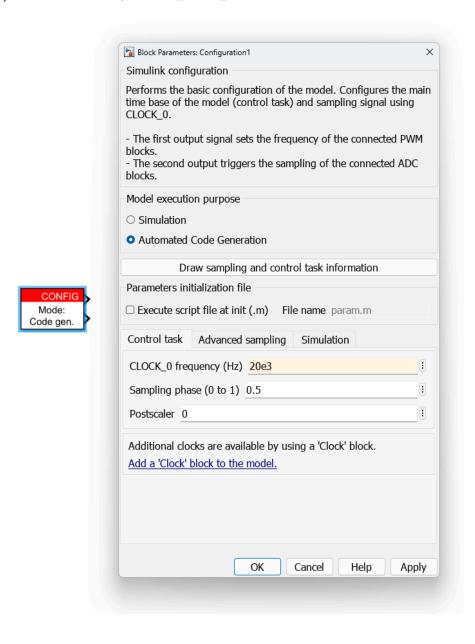

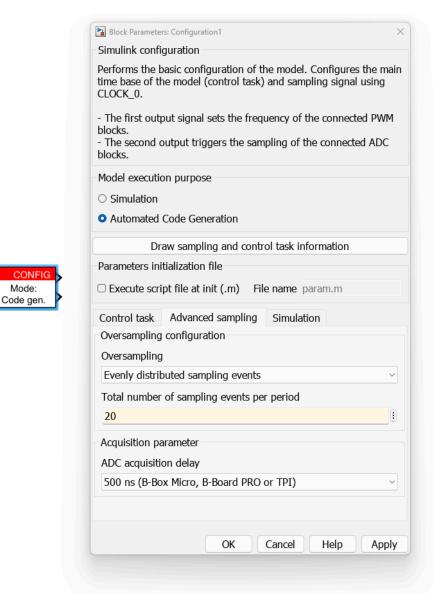

#### **CPU-side implementation**

The CPU-side code provided below has been implemented using Simulink and the imperix <u>ACG SDK</u>. To make these variables available during run-time, the *gain* is set using a <u>tunable parameter</u> and the *adc\_raw* and *result* are read using <u>probes</u>. These 3 values are encoded as **single** (32-bit single-precision floating-point). The MATLAB Function blocks *single2sbo* and *sbi2single* allow to easily map *single* values to <u>SBI</u> and <u>SBO</u> blocks.

Click to download PN159\_Getting\_Started\_With\_FPGA.slx

#### **FPGA-side implementation**

As mentioned earlier, only standard Xilinx Vivado IP blocks are used to implement the algorithm in this example. The **PN159\_vivado\_design.pdf** file below shows the full Vivado FPGA design. Here are the step-by-step instructions to reproduce it.

#### Click to download PN159\_vivado\_design.pdf

- 1. Add a block to convert the int16 data of ADC\_00 to a single-precision floating-point

- 1. Right-click somewhere in the block design and choose **Add IP...**

- 2. Search for the *Floating-point* IP, drag-and-drop it on the diagram.

- 3. Rename it as int16\_to\_single.

- 4. Double-click on the *int16\_to\_single* block. In the pop-up window, select the **Fixed-to-float** operation, change Auto to Manual and set the precision type to Custom. Then, set the integer width to 16, and select **Single** as precision for the result.

#### 2. Add the multiplier block

- 1. Add another Floating-point IP and rename it as single\_multiplier.

- 2. Double-click on the block.

- 3. Select the **Multiply** operation and **Single** input.

#### 3. Broadcast one stream to two streams

- 1. Right-click somewhere in the block design and choose Add IP...

- 2. Search for the AXI4-Stream Broadcaster, drag it and drop it on the diagram.

- 3. Keep all options to auto.

AXI4-Stream Broadcaster

#### 4. Connect all the blocks as follow:

- M\_AXIS\_ADC\_00 to S\_AXIS\_A of int16\_to\_single

- M\_AXIS\_RESULT of int16\_to\_single to S\_AXIS of axis\_boradcaster\_0

- M00\_AXIS of axis\_broadcaster\_0 to S\_AXIS\_FPGA2CPU\_00

- M01\_AXIS of axis\_broadcaster\_0 to S\_AXIS\_B of single\_multiplier

- M\_AXIS\_CPU2FPGA\_00 to S\_AXIS\_A of single\_multiplier

- M\_AXIS\_RESULT of single\_multiplier to S\_AXIS\_FPGA2CPU\_01

- o clk\_250\_mhz to all aclk inputs

- **nReset\_sync** to **aresetn** of *axis\_broadcaster\_0*

#### 5. Finally, the design can be synthesized and the bitstream generated. Click Generate bitstream. It will launch the synthesis, implementation and bitstream generation.

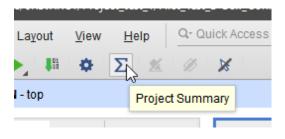

6. Always make sure that your design meets the timing requirements! This information is available from the Project Summary To learn more please visit the Xilinx documentation on <u>Timing Closure</u>.

Opening the Vivado Project Summary

7. If the timing requirement are met, click on **File** → **Export** → **Export Bitstream File...** to save the bitstream somewhere on the computer.

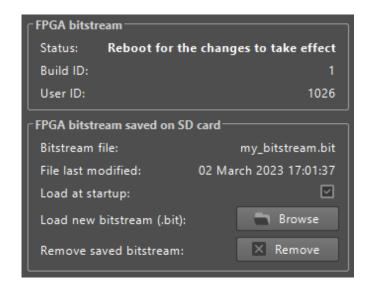

#### Loading the bitstream into the imperix controller

Using <u>imperix Cockpit</u>, the bitstream is loaded into the imperix controller device from the **target configuration** window.

Loading an FPGA bitstream in the controller

## **Experimental validation**

Finally, the CPU code is generated from the Simulink model and loaded into the device, as explained in the <u>programming and operating imperix controllers</u> page.

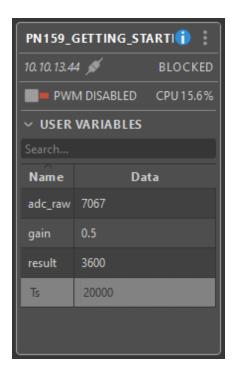

To test the design, a sinusoidal signal is fed to the analog input of the B-Box. Then, using Cockpit's scope, the  $result = 0.5*adc\_raw$  is observed:

# **Going further**

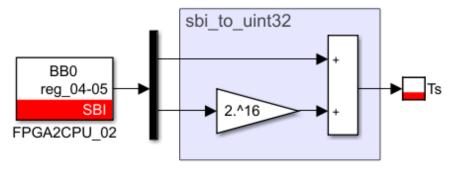

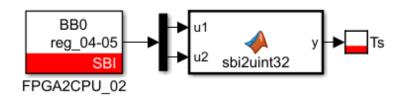

## Testing M\_AXIS\_Ts

This section goes a bit further in the demonstration of the provided AXI4-Stream M\_AXIS\_Ts to help understand the **M\_AXIS\_Ts interface**, and show how to **transfer an uint32** value from the FPGA to the CPU.

The modification of the FPGA bitstream is quite simple: simply connect **M\_AXIS\_Ts** to **S\_AXIS\_FPGA2CPU\_02** as shown in orange on the image below. This allows reading the sample time Ts value from the CPU.

On the CPU, to retrieve the Ts value, the value is read from **S\_AXIS\_FPGA2\_CPU\_02** (SBI\_04 and SBI\_05). Because the value is a *32-bit unsigned integer*, the transformation is different from before as shown below.

#### **Option 1**

concatenate two uint16 to form a uint32

#### **Option 2**

function y = sbi2uint32(u1,u2)

y = uint32(0); % fix compiled size of output

y = typecast([uint16(u1) uint16(u2)], 'uint32');Code language: Matlab (matlab)

Finally, using Cockpit, the result can be observed. If the control task frequency (CLOCK\_0) is set to 50 kHz, then **M\_AXIS\_Ts** will return 20'000 ns.

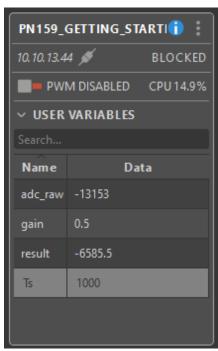

If CLOCK\_0 is kept at 50 kHz and the oversampling is activated with an oversampling ratio of 20, then **M\_AXIS\_Ts** will return 1000 ns, which corresponds to the actual sampling period.

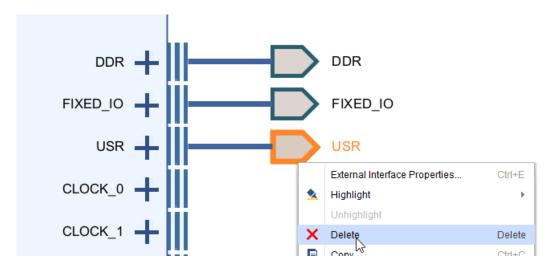

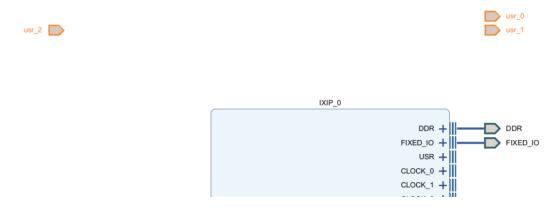

# **Using the USR pins**

The imperix controllers feature 36 user-configurable 3.3V I/Os (the **USR** pins) that are directly accessible from the FPGA. Their physical locations are available in the <u>B-Board PRO datasheet</u> and <u>B-Box RCP datasheet</u>.

By default, the USR pins are connect to the imperix IP. Currently they are only used to communicate with the with the <u>motor interface</u>. If the motor interface is not used, then the USR port can safely be deleted.

These pins are then available for other use. The screenshot show an example where the USR pins 0, 1, and 2 are used.

The constraints\sandbox\_pins.xdc must be edited accordingly. As shown below, we recommend commenting (#) the unused pins to avoid generated unnecessary warning the Vivado.For more information on constraints in Xilinx FPGA please refer to the <u>using constraints in Vivado Design Suite</u> user guide.

When top level ports are modified, the block design wrapper must be updated accordingly to reflect the changes. To make sure top\_wrapper.vhd is up-to-date, the recommended procedure is to remove the current one and generate a new one:

- Right click on top wrapper -> Remove File from Project...

- Check "Also delete the project file from disk" -> OK

- Right click on top -> Create HDL Wrapper

The <u>FPGA-based SPI communication IP for ADC</u> page shows an example where USR pins are used to drive an external ADC using the SPI protocol.

#### **Additional tutorials**

The page <u>custom FPGA PWM modulator</u> explains how to **drive PWM outputs** or to use the **CLOCK interfaces** through a simple example. The PWM modulator sources are provided as VHDL, as a Xilinx System Generator model, and as a MATLAB HDL Coder model.

The page <u>high-level synthesis for FPGA</u> developments shows how to integrate **HLS-generated IPs** in an FPGA control implementation using a **PI-based current control** of a buck power converter as an example.

Back to FPGA development homepage