### **Custom PWM modulator implementation in FPGA**

TN141 | Posted on June 10, 2021 | Updated on May 7, 2025

Benoît STEINMANN Software Team Leader imperix • in

#### Table of Contents

- Design choices for the FPGA-based PWM modulator

- How to implement pulse-width modulation in FPGA?

- o 1) FPGA PWM using Xilinx System Generator

- o 2) FPGA PWM using HDL Coder

- o 3) FPGA PWM using VHDL

- Testing the FPGA-based PWM module in simulation

- Integrating the PWM modulator into the Xilinx FPGA

- o Description of the FPGA-based PWM modulator example

- o <u>CPU-side implementation</u>

- o FPGA-side implementation using Vivado

- Experimental validation

- · Going further

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents how to implement a **custom PWM modulator** in the Xilinx **FPGA** of the imperix controller (<u>B-Box RCP</u> or <u>B-Board PRO</u>).

The presented modulator uses FPGA pulse-width modulation with a triangular carrier. The sources of this example can be re-used in an FPGA-based power converter control design. Alternatively, it can be used as a starting point to develop more complex custom PWM modulators.

The first section of this page explains how the PWM module fits into an FPGA-based control design as well as the FPGA design of the pulse-width modulation. Next, the actual implementation of the FPGA modulator is presented using 3 different tools:

- 1. the Xilinx blockset for Simulink System Generator

- 2. the Simulink add-on MATLAB HDL Coder

- 3. hand-written VHDL coding

Then, a Simulink testbench is built to test the FPGA design in simulation. Finally, the modulator is integrated into the imperix controller FPGA to be validated.

This page addresses advanced content for users who require implementing converter control algorithms with FPGA logic or implementing non-standard modulation techniques.

For most use-cases, using CPU-based control and the pre-implemented <u>carrier-based PWM modulators</u> of the imperix library is widely sufficient and should be preferred.

To find all FPGA-related notes, you can visit FPGA development homepage.

# Design choices for the FPGA-based PWM modulator

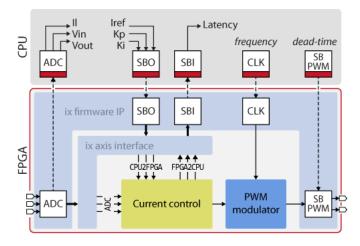

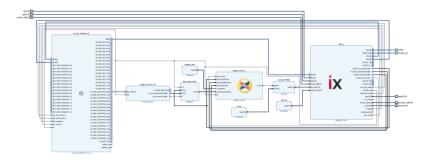

The Pulse Width Modulator (PWM) is intended to be used in a larger design such as the FPGA-based buck converter control example shown in the image below. The **imperix firmware IP** and **ix axis interface** are explained in the <u>getting started with FPGA control</u> page and the **current control** module is presented in the <u>high level synthesis for FPGA</u> tutorial.

Power converter control in an imperix controller

The FPGA-based PWM modulator must be connected to one of the 4 clock generators (CLK). In this example, the CLK allows synchronizing the CPU control task with the PWM carrier. For further details on the CLK FPGA signals, please refer to the "CLOCK interface" section of <a href="imperix firmware IP">imperix firmware IP</a> user guide.

The Sandbox PWM (SB-PWM) block makes it possible to drive the same PWM output chain as that used by other modulators (CB-PWM, PP-PWM, DO-PWM, and SS-PWM). This allows the user to generate complementary signals with dead-time, use the standard activate and deactivate functions and rely on the protection mechanism that blocks PWM outputs when a fault is detected.

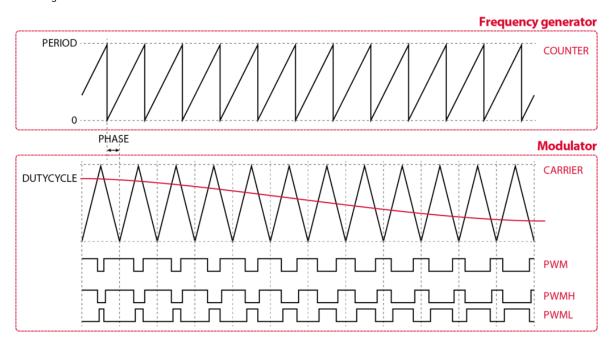

The figure below shows how the FPGA modulator operates. The pulse-width modulation is obtained by comparing a duty cycle value with the triangular carrier wave.

PWM modulator based on a triangular carrier

The duty cycle can be updated using a **single rate** or **double rate**. When using the single-rate update, the duty cycle value is applied when the triangular carrier reaches its minimum. With the double-rate update, the duty cycle is updated twice per period: when the carrier reaches its maximum and when it reaches its minimum.

In summary, this FPGA PWM modulator behaves as a carrier-based PWM (<u>CB-PWM</u>) modulator that is configured with a triangular carrier, and a phase of 0.

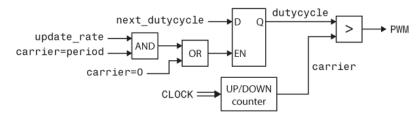

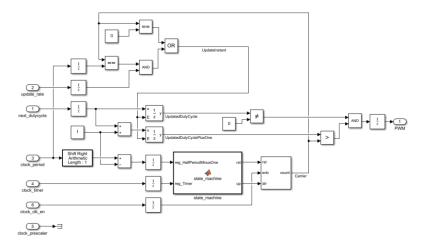

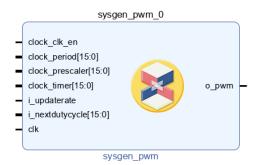

The FPGA-based PWM module is shown below. The screenshot shows the IP generated with <u>System Generator</u>, but the input and output ports are identical when using MATLAB <u>HDL Coder</u> or VHDL. The ports are the following:

- CLOCK: the clock interface that is meant to be connected to the CLOCK output of imperix firmware IP. It contains:

- ∘ CLOCK\_prescaler, the CLK\_timer ticking rate, 1 tick = (4 ns/CLK\_prescaler)

- o CLOCK\_clk\_en, asserted to indicate a new tick.

- $\circ~{\tt CLOCK\_period},$  the PWM period in ticks

- CLOCK\_timer, a counter that goes from 0 to CLK\_period-1

- next\_dutycycle: the next duty cycle to be updated. This signal is a 16-bit unsigned integer with a unit of ticks.

- update\_rate: controls the update rate. '0' is single-rate and '1' is double-rate.

- pwm: the pulse-width modulation output signal

FPGA-based PWM module developed using Xilinx System Generator

Below is shown the high-level schematic of the FPGA-implemented PWM modulator. The *duty cycle* is stored in a register, whose enable port is controlled by the *update rate*. The triangular carrier is generated from the *CLOCK* input using an up/down counter that behaves as follows:

- it resets each time CLOCK\_timer is equal to zero

- after a reset, it counts UP until CLOCK\_timer reaches CLOCK\_period/2

- then, it counts down until it reaches zero.

High-level schematic of the PWM block

### How to implement pulse-width modulation in FPGA?

This section provides 3 possible approaches for implementing the FPGA PWM modulator, using Xilinx System Generator, MATLAB Simulink HDL Coder, or hand-written VHDL.

## 1) FPGA PWM using Xilinx System Generator

The implementation of the FPGA PWM modulator using **Xilinx System Generator** is given below. The sources are available on the <u>System Generator introduction</u> page.

Please note the following important points:

- 1. The input and output ports are represented with *Gateway in* and *Gateway out* blocks. The sample time is set to **4ns** to ensure that the model represents the real behavior of the FPGA.

- 2. All the input signals are registered to improve performance.

- 3. In System Generator, users can configure the latency for each block. If there is a timing violation in the generated IP, try to increase the latency or insert registers between operations.

- 4. The carrier is generated using a free-running counter and a state machine that controls the counter. System Generator provides *MCode* block where users can convert MATLAB code to VHDL. The MATLAB code for the state machine is given below.

FPGA-based modulator designed using Xilinx System Generator

```

function [up,rst] = state_machine(reg_HalfPeriodMinusOne, reg_Timer)

persistent state, state = xl_state(0,{xlUnsigned, 1, 0});

```

```

% default value

up = 1;

rst = 0;

switch state

case 0 % counting up

up = 1;

rst = 0;

if reg_Timer > reg_HalfPeriodMinusOne

state = 1;

case 1 % counting down

up = 0;

if reg_Timer == 0

state = 0:

rst = 1;

else

rst = 0;

end

endCode language: Matlab (matlab)

```

# 2) FPGA PWM using HDL Coder

The implementation of the FPGA PWM modulator using **HDL Coder** is given above. The sources are available on the <u>MATLAB HDL Coder introduction</u> page.

Please note the following important points:

- 1. The input and output ports are represented with Simulink input and output ports. The sample time is set to **4ns** to ensure the model represents the real behavior in FPGA.

- 2. The *delay* block can be used to represent the register in FPGA.

- 3. The carrier is generated using a free-running counter and a state machine that controls the counter. Here, the state machine is implemented using a *MATLAB Function* block. The MATLAB code for the state machine is given below.

FPGA-based PWM module designed using MATLAB HDL Coder

function [rst, up] = state\_machine(reg\_HalfPeriodMinusOne, reg\_Timer)

```

% define states

state_up = uint8(0);

state_down = uint8(1);

persistent state

if isempty(state)

state = state_up;

end

% default value

up = true;

rst = false;

switch state

case state_up % counting up

up = true;

rst = false;

if reg_Timer > reg_HalfPeriodMinusOne

state = state_down;

```

```

end

```

```

case state_down % counting down

up = false;

if reg_Timer == 0

state = state_up;

rst = true;

else

rst = false;

end

end

Code language: Matlab (matlab)

```

## 3) FPGA PWM using VHDL

The following VHDL code implements the FPGA pulse-width modulation design but in hand-written VHDL.

```

VHDL implementation of the carrier-based PWM modulator

```

```

-- Create Date: 10/02/2021

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity UserCbPwm is

Port (

CLOCK_period : in std_logic_vector(15 downto 0);

CLOCK_timer : in std_logic_vector(15 downto 0);

CLOCK_prescaler : in std_logic_vector(15 downto 0);

CLOCK_clk_en : in std_logic;

-- must be between 0 and CLOCK_period

-- loaded when the carrier reaches zero

i_nextDutyCycle : in std_logic_vector(15 downto 0);

i_enableDoubleRate : in std_logic;

o_carrier : out std_logic_vector(15 downto 0);

o_pwm : out std_logic;

clk_250_mhz : in std_logic

);

end UserCbPwm;

architecture impl of UserCbPwm is

ATTRIBUTE X_INTERFACE_INFO : STRING;

ATTRIBUTE X_INTERFACE_INFO of clk_250_mhz: SIGNAL is "xilinx.com:signal:clock:1.0 clk_250_mhz CLK";

ATTRIBUTE X_INTERFACE_INFO of CLOCK_period:

SIGNAL is "imperix.ch:ix:clock_gen_rtl:1.0 CLOCK period"; SIGNAL is "imperix.ch:ix:clock_gen_rtl:1.0 CLOCK timer";

ATTRIBUTE X_INTERFACE_INFO of CLOCK_timer:

ATTRIBUTE X_INTERFACE_INFO of CLOCK_prescaler: SIGNAL is "imperix.ch:ix:clock_gen_rtl:1.0 CLOCK prescaler";

SIGNAL is "imperix.ch:ix:clock_gen_rtl:1.0 CLOCK clk_en";

ATTRIBUTE X_INTERFACE_INFO of CLOCK_clk_en:

attribute X_INTERFACE_MODE : string;

attribute X_INTERFACE_MODE of CLOCK_timer : signal is "monitor";

signal reg_Pwm : std_logic;

signal reg_Carrier : unsigned(15 downto 0);

signal reg_ClkEnable : std_logic;

signal reg_HalfPeriodMinusOne : unsigned(15 downto 0);

signal reg_DutyCycle : unsigned(15 downto 0);

signal reg_DutyCyclePlusOne : unsigned(15 downto 0);

signal reg_Timer : unsigned(15 downto 0);

type t_CarrierStates is (COUNTING_UP, COUNTING_DOWN);

signal reg_CarrierState: t_CarrierStates;

begin

o_carrier <= std_logic_vector(reg_Carrier);</pre>

o_pwm <= reg_Pwm;

P_INPUT_SAMPLING : process(clk_250_mhz)

```

```

begin

if rising_edge(clk_250_mhz) then

reg_Timer <= unsigned(CLOCK_timer);</pre>

reg_ClkEnable <= CLOCK_clk_en;</pre>

reg_HalfPeriodMinusOne <= shift_right(unsigned(CLOCK_period), 1) - 1;</pre>

- update the duty-cycle when the carrier hits zero

if reg_Carrier = 0 or (i_enableDoubleRate = '1' and reg_Carrier = unsigned(CLOCK_period)) then

reg_DutyCycle <= unsigned(i_nextDutyCycle);</pre>

reg_DutyCyclePlusOne <= unsigned(i_nextDutyCycle) + 1;</pre>

end if:

end if;

end process P_INPUT_SAMPLING;

P_TRIANGLE_CARRIER: process(clk_250_mhz)

begin

if rising_edge(clk_250_mhz) then

-- reg_ClkEnable serves to slow down the logic if the CLOCK_prescaler is used

-- it is used only if the frequency is lower than 3.8 kHz

if reg_ClkEnable = '1' then

if reg_CarrierState = COUNTING_UP then

reg_Carrier <= reg_Carrier + 2;</pre>

if reg_Timer >= reg_HalfPeriodMinusOne then -- minus one because well go in counting down in next clock

reg CarrierState <= COUNTING DOWN;</pre>

end if;

else -- reg_CarrierState = COUNTING_DOWN

if reg_Carrier >= 2 then

reg_Carrier <= reg_Carrier - 2;</pre>

end if;

if reg_Timer = 0 then

reg_CarrierState <= COUNTING_UP;</pre>

reg_Carrier <= (others => '0');

end if;

end if;

end if;

end if;

end process P_TRIANGLE_CARRIER;

P_OUTPUT: process(clk_250_mhz)

begin

if rising_edge(clk_250_mhz) then

if (reg_DutyCycle /= 0) AND (reg_DutyCyclePlusOne > reg_Carrier) then

reg_Pwm <= '1';

else

reg_Pwm <= '0';

end if;

end if;

end process P OUTPUT;

end impl; Code language: VHDL (vhdl)

```

# **Testing the FPGA-based PWM module in simulation**

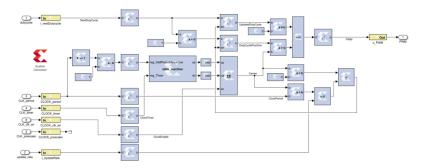

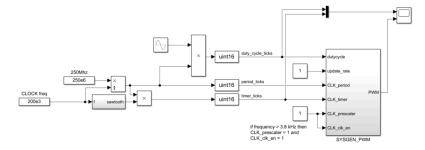

The following test bench is used to validate the proper functioning of the FPGA pulse-width modulation with a Simulink simulation. The screenshots below show the test of PWM using the Xilinx System Generator implementation, but the testbench is identical for testing the MATLAB HDL Coder implementation.

Simulation test bench for the FPGA-based PWM block

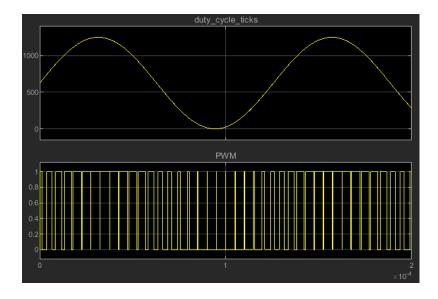

The testbench generates CLOCK signals that are identical to the interface of the *imperix firmware* IP. The CLOCK frequency is set to 200 kHz. A sinusoidal signal ranging from 0 to CLOCK\_period (in ticks) is connected to the *dutycycle* input. The following plot validates that the resulting PWM has a frequency of 200 kHz and that its duty cycle varies from 0 to 1 following the sinusoid.

As shown below, the behavior of internal signals of the PWM module can also be inspected by adding scopes inside the Xilinx System Generator design. System Generator will complain and show red (!). It does not cause any problem during simulation but it is important to remove any scope before generating the FPGA IP.

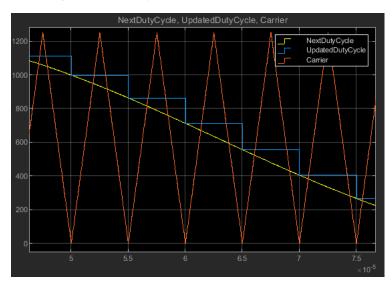

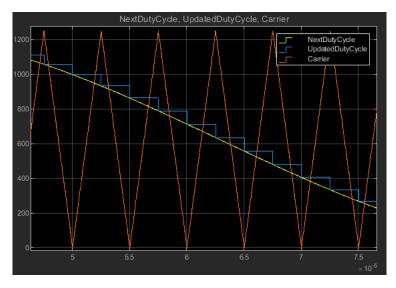

The internal signal UpdatedDutyCycle is the actual value compared to the triangular carrier to generate the PWM signal. Changing the constant signal applied to the update\_rate input allows selecting between *single-rate* update (0) and *double-rate* update (1). These two modes are documented in the standard <u>carrier-based PWM block help</u>. Observing internal signals allows checking that the UpdatedDutyCycle behaves according to the selected update rate mode.

Duty cycle update in single-rate update mode

Duty cycle update in double-rate update mode

### Integrating the PWM modulator into the Xilinx FPGA

## **Description of the FPGA-based PWM modulator example**

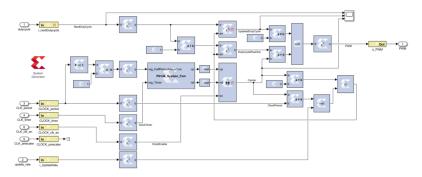

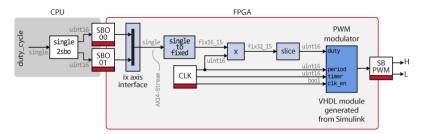

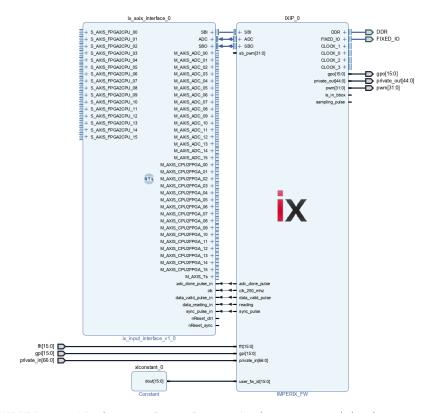

The FPGA design illustrated below is used to test the generated FPGA PWM modulator. Its purpose is to manually select the duty cycle of the modulator from a PC by using <a href="Imperix Cockpit">Imperix Cockpit</a>. To do so, a <a href="tunable-parameter">tunable-parameter</a> block is used on the CPU. It is configured with the name <a href="duty\_cycle">duty\_cycle</a> and the data type <a href="single">single</a>. This value is transferred from the CPU to the FPGA using the <a href="CPU2FPGA\_00">CPU2FPGA\_00</a> interface (SBO\_00 and SBO\_01) as explained in the <a href="getting-started with FPGA control">getting-started with FPGA control</a> page. In the FPGA, this single-precision duty-cycle is transformed into an integer value in ticks as follow:

- The 32-bit single-precision floating-point value is transformed into a 16-bit fixed-point value with an integer width of 1-bit and a fraction width of 15-bit (fix16\_15). This repartition has been chosen because the duty cycle is expected to range between 0.0 and 1.0 so only 1-bit is required on the integer part.

- To obtain a value in *ticks*, the result of the previous step is multiplied by CLOCK\_period. The result of the multiplication of a fix16\_15 with a uint16 is a fix32\_15 (32-bit, 17-bit integer part, and 15-bit fractional part).

- Finally, only the 16 first bits of this result are used as the duty cycle input of the FPGA PWM modulator IP.

The CLOCK\_0 will be used as a clock reference for the FPGA pulse-width modulation, which means that the PWM modulator will run at the same frequency as the CPU control task and that both will stay synchronized. (That is because the CPU interrupt rate is always defined by CLOCK\_0.)

On the imperix firmware IP, the sb\_pwm[31:0] port provides access to the same PWM output chain as that used by other modulators (CB-PWM, PP-PWM, DO-PWM and SS-PWM). This allows the user to generate complementary signals with dead-time, use the standard activate and deactivate functions and rely on the protection mechanism that blocks PWM outputs when a fault is detected.

When driving a PWM channel (two pseudo-complementary signals with dead time), the user only needs to generate the HIGH signal, which must be connected to the appropriate sb\_pwm input (sb\_pwm[0], sb\_pwm[2], sb\_pwm[4], etc.). Another example of such a configuration is available in the <u>FPGA-based hysteresis current control</u> example

Imperix strongly discourages the user from directly driving the top-level pwm port, as this would bypass the enable/disable mechanism! Instead, the SB-PWM driver is meant to provide proper access to PWM outputs, which should be used in all cases. This is critical since this mechanism also handles **fault management**!

# **CPU-side implementation**

As with any FPGA-based implementation, a CPU code is still required to configure the imperix IP and define real-time variables accessible from the various <u>Cockpit modules</u>. In the current example, the CPU code

- configures the frequency of CLOCK\_0,

- configures the Sandbox PWM driver,

- declares the duty\_cycle variable and transmits it to the FPGA through the SBO interface.

#### Using ACG SDK on Simulink

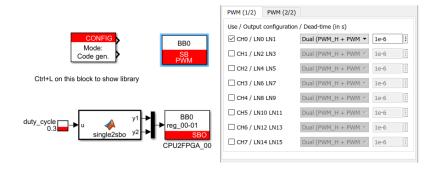

The frequency of CLOCK\_0 is defined in the <u>Configuration block</u>, and the duty\_cycle (float) variable is created using a <u>tunable parameter</u> block. It is then mapped to <u>M\_AXIS\_CPU2\_FPGA\_00</u> using the MATLAB Function block <u>single2sbo</u> (as introduced in <u>Getting started with FPGA control development</u>).

The <u>SB-PWM block</u> is used to configure and activate/deactivate the output PWM **channel 0 (CH0)** (lane #0 and lane #1). The output is configured as **Dual (PWM\_H + PWM\_L)** with a **deadtime** of 1 µs. This configuration expects a PWM signal coming to **sb\_pwm[0]** input of the *imperix firmware* IP and will automatically generate the complementary signals with the configured deadtime.

Click to download the Simulink model

#### **Using CPP SDK**

The equivalent functionalities can also be implemented in C code, using <u>CPP SDK</u>. The corresponding code is available for download below.

Click to download the C code example

### **FPGA-side implementation using Vivado**

The TN141\_vivado\_design.pdf file below shows the full Vivado FPGA design. Here are the step-by-step instructions to reproduce it.

#### Click to download TN141\_vivado\_design.pdf

1. Create an FPGA control implementation starter template by following the Getting started with FPGA control implementation.

2. Add the FPGA PWM IP into your Vivado project. System Generator is taken as an example but the steps are identical for a VHDL or an HDL Coder module.

3. Add a *Floating-point* IP and select the **Float-to-fixed** operation. Select **Single** precision for input and **Integer Width 1, Fraction Width 15** (fix16\_15) for output. This module will convert the *duty cycle* sent by CPU from single to fix16\_15.

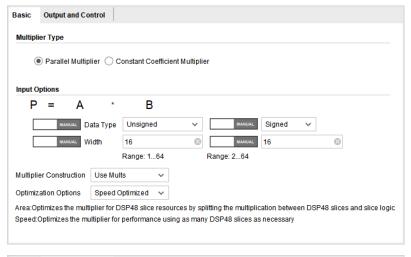

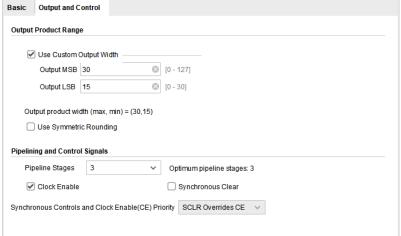

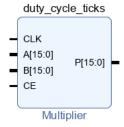

- 4. Add a **Multiplier IP** and set the configuration as shown below.

- $\circ~$  The input A is connected to the CLOCK\_period ~ so it is set to 16-bit unsigned

- o The input B is connected to the fixed-point duty cycle so it is set to 16-bit signed

- o The output range is set to return only the 16 first bits of the integer part of the result

- The clock enable (CE) input is enabled and will be connected to the *tvalid* output of the *single\_to\_fix16\_15* IP output. This way, the multiplication is performed synchronously with the data coming from the AXI4-Stream.

5. Add a Constant IP to set all the 31 unused sb\_pwm outputs to '0'. Set its Const Width to 31 and its Const Val to 0.

6. Add a Concat IP. It will serve to concat the pwm output of the PWM IP with the zeros of the Constant IP.

- 7. Connect the pins as follows:

- $\circ~$  all the  ${\tt CLOCK\_0}$  signals of the  ${\it imperix\ firmware\ IP}$  signals to the PWM block

- M\_AXIS\_CPU2FPGA\_00 to S\_AXIS\_A of single\_to\_fix16\_15

- o CLOCK\_0\_period to A of the Multiplier

- o tdata of M\_AXIS\_RESULT of single\_to\_fix16\_15 to B of the Multiplier

- tvalid of M\_AXIS\_RESULT of single\_to\_fix16\_15 to CE of the Multiplier

- o P of the Multiplier to i\_nextdutycycle

- o **o\_pwm** of the *PWM* IP to **In0** of the *Concat* IP

- o dout of the 31-bit to zero Constant IP to In1 of the Concat IP

- o dout of the Concat IP to the sb\_pwm input of the imperix firmware IP

- o all the IP clocks to clk\_250\_mhz

And finally, the design can be synthesized and the bitstream generated:

- 1. Click Generate bitstream. It will launch the synthesis, implementation and bitstream generation

- 2. Once the bitstream generation is completed, click on **File** → **Export** → **Export Bitstream File...** to save the bitstream somewhere on your computer.

### **Experimental validation**

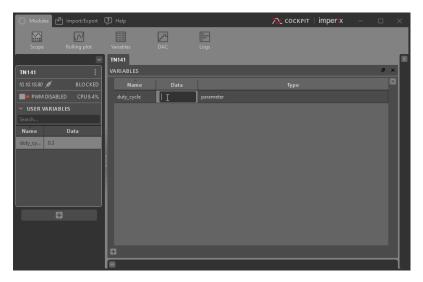

The bitstream can be generated and loaded into the device using <u>Cockpit</u>, as explained in the <u>Getting started with FPGA control implementation</u> page. Then, the Simulink model *TN141\_CPU\_side.slx* can be built and launched as explained in the <u>Programming and operating imperix controllers</u> getting started page.

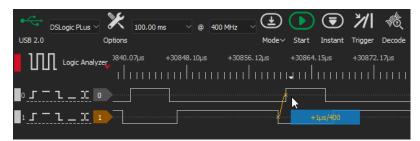

Using the <u>Variables module</u> of Cockpit, the *duty\_cycle* variable can be changed in real-time. After enabling the PWM outputs, the PWM signals at the output CH0 (lanes 0 & 1) can be observed using an oscilloscope or a logic analyzer.

imperix Cockpit user interface

The screenshot below shows the measured PWM signals using a logic analyzer, as expected the measured signals are complementary 50 kHz PWM signal with a duty cycle of 30% and a dead time of  $1 \mu s$ .

# **Going further**

The <u>high-level synthesis for FPGA developments</u> page re-uses this FPGA PWM modulator in a **PI-based current control** of a **buck converter** scenario. It shows how to integrate and connect **HLS-generated IPs** in a realistic FPGA power converter control implementation.

Back to <u>FPGA development homepage</u>