FPGA CUSTOMIZATION

FPGA-BASED POWER CONVERTER CONTROL IMPLEMENTATION

In power electronics, advanced power converter control techniques often require that part of the converter ontrol algorithms are implemented on FPGA. With imperix converter controllers, this is made easy since FPGA-based control implementation is possible with both software development kits.

This enables users to augment the set of available functions, such as new modulation algorithms, interfaces for external peripherals, or offload computation to the FPGA.

FPGA-BASED CONTROL FOR POWER ELECTRONICS

Imperix controllers are based on the powerful AMD/Xilinx Zynq family. They embed two 1GHz ARM processors (DSPs), as well as a Kintex-grade FPGA section. In most cases, power electronic engineers only develop control algorithms for the main processing core (DSP), while the FPGA section is automatically loaded with pre-configured peripherals.

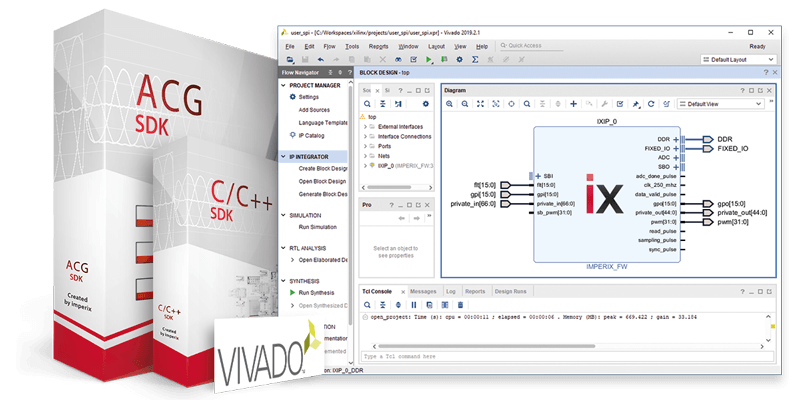

That said, the FPGA section is always freely editable so that challenging applications can leverage the power of unused FPGA resources for specific power converter control tasks. To this end, relying on all the Xilinx Vivado Design Suite tools and IPs, working with imperix programmable controllers is as simple as programming any other Xilinx FPGA. Furthermore, communication with the DSP cores is facilitated, thanks to pre-written interfaces (both DSP and FPGA sides) and users can rely on several application examples and templates.

Extensive FPGA capabilities

The pre-implemented imperix firmware only uses approximately 50% of the FPGA logic resources and 50% of the physical ports. As such, the unused logic represents most of the FPGA area, entirely available to the user.

No additional license

The FPGA firmware can be edited and customized without needing any additional license. This capability is already included with both the ACG SDK or CPP SDK and for any imperix controller.

Easy interfacing

Pre-written interface blocks are available on both the DSP and FPGA sides, so that users can easily integrate their own FPGA developments inside the existing framework, even when working from Simulink or PLECS.

MAIN BENEFITS

- Complete freedom: The unused FPGA logic and I/O ports can be used as the user sees fit.

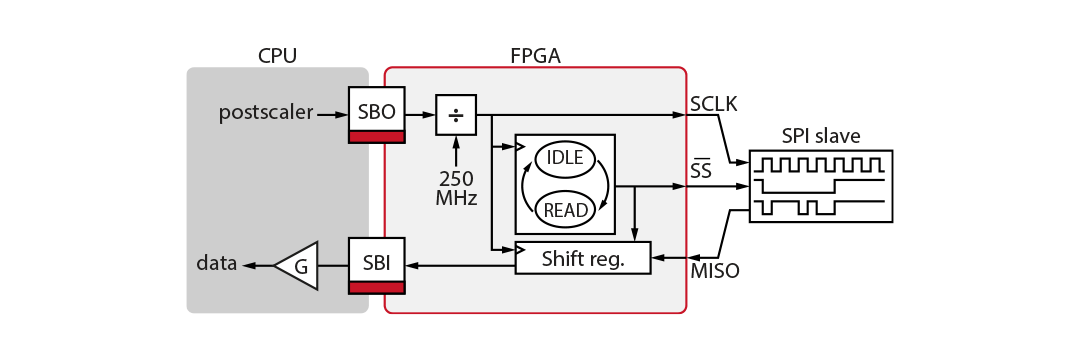

- High performance: The 250 MHz base clock and FPGA parallel architecture allow for very fast algorithms.

- Easy interfacing: Exchanging data between CPU and FPGA is made easy using the provided drivers.

- Free of charge: The Xilinx Vivado software and the FPGA programmability come at no additional cost.

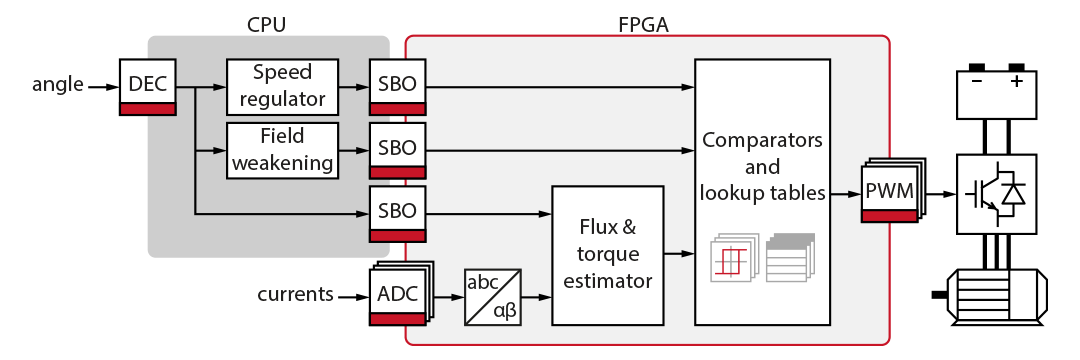

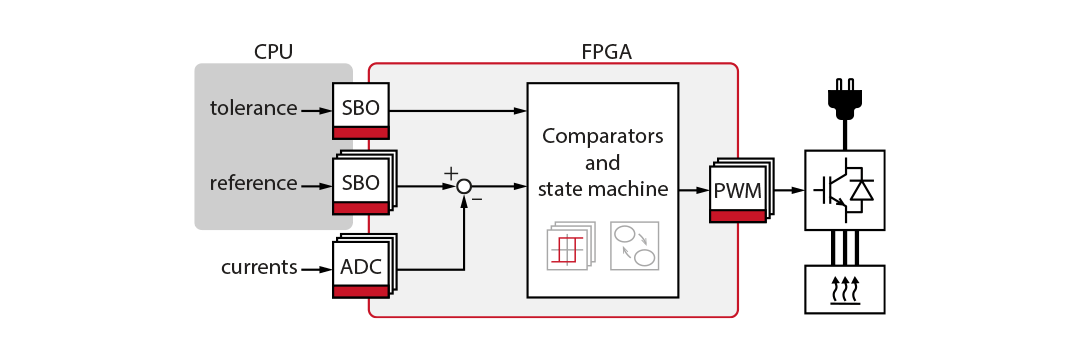

Separate the control between DSP and FPGA, which enables the implementation of faster control loop or custom modulators.

Use your preferred workflow and language. High-level description and synthesis are also possible, e.g. using Matlab HDL Coder or Xilinx Vivado HLS.

Integrate your design to the existing firmware and have access to the ADC, PWM, I/Os, (and much more) from the FPGA. Communication with the CPU is also facilitated.

Flash your customized firmware directly using Cockpit and an Ethernet connection. No need for an additional cable or to open the box.

FPGA RAPID PROTOTYPING

for power electronics

- Open the provided template

- Instantiate your module

- Connect it to the imperix IP using the Xilinx Vivado environment

The imperix IP provides a set of 128 registers named SBI and SBO. On the DSP side, drivers are provided to read or write in these registers in all simplicity. The communication is completely transparent to the user.

To access the outside world, 36x high-speed 3.3V pins can freely be used (USR pins) in addition to all other peripherals.

![]() Hover to find out more.

Hover to find out more.

DSP+FPGA-BASED CONVERTER CONTROL

DSP-SIDE WORKFLOW

The Xilinx Zynq holds a dual-core processor. The first core runs Linux and is in charge of the overall supervision. The second core runs our dedicated OS and can be programmed by the user with application-specific power converter control algorithms.

The DSP code can be written in C/C++ (CPP SDK) or generated using a graphical environment such as Simulink or PLECS (ACG SDK).

Matlab Simulink

The Simulink blockset allows to program the device without any code and provides an accurate offline simulation.

Plexim PLECS

Imperix provides a blockset for the PLECS software too, which also supports code generation and offline simulation.

C/C++ code

For maximal code optimization and flexibility, the CPU code can be directly coded in C/C++.

FPGA-SIDE WORKFLOW

The standard FPGA firmware contains the pre-implemented peripherals (ADC, PWM,…) and networking logic. Users can customize this firmware by augmenting it with their own programmable logic design using the Xilinx Vivado Design Suite.

There are many ways to create a FPGA design, from HDL code (VHDL/Verilog) to C++ or even graphical interface blocks.

HDL langages (VHDL/Verilog)

For complete control over the design, VHDL or Verilog can be used to describe the FPGA logic.

Xilinx Vivado HLS (C++)

To implement complex algorithms, tools such as Vivado HLS can be used to easily generate HDL code from C++.

Matlab HDL Coder

Matlab HDL Coder allows generating HDL code directly from MATLAB functions, Simulink models or Stateflow charts.

TRANSPARENT NETWORKING ACROSS CONTROLLERS

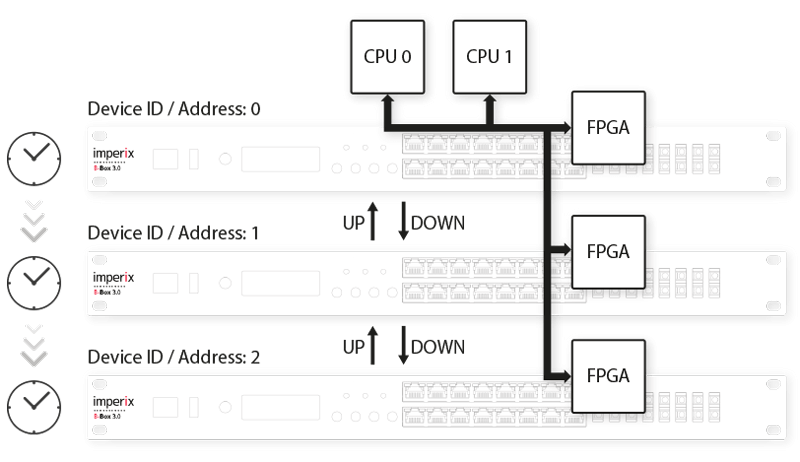

All imperix controllers, except the B-Box Micro, are compatible with networked control operation. This enables engineers to address complex systems with demanding I/O requirements.

Devices pre-addressing

A device ID ranging from 0 to 63 is automatically attributed to each device by the BBOS operating system.

Full-duplex transfers

5 Gbps optical links are used for inter-device communication. Moreover, UP and DOWN traffic works in a full-duplex fashion for maximal performance.

Native synchronization

All the networked devices are synchronized with an accuracy of ±2 ns to imperix Real Sync technology. Absolutely zero clock drift!

No need to worry about device addressing

To increase the I/Os capability, up to 64 devices can be connected, in a totally transparent manner. Indeed, the device addressing is entirely managed by the real-time operating system BBOS.

Furthermore, all units are natively synchronized with an accuracy of ±2 ns thanks to imperix’s Real Sync technology. This allows using all FPGAs and I/Os as if they simply belonged to the same controller hardware!

Slaves can integrate processing tasks

In a multi-controllers setup, normally only one DSP oversees the overall execution, inside the master. Nevertheless, thanks to the FPGA’s direct access to the ADC results and PWM outputs, local control loops can be implemented within slave FPGAs too.

Furthermore, soft-processors can be instantiated in the FPGA (e.g. Xilinx MicroBlaze), which can be programmed and debugged just like a standard DSP, making things even easier!

WANT TO KNOW MORE?

For all questions related to our software, feel free to get in touch with our technical team. We’re here to help! Online demos can also be organized upon request.

Alternatively, you can always download and install the software. As our licenses are hardware-related, our software is essentially unrestricted and all features can be tested free of charge.