Accessing the USR pins in the FPGA sandbox

Most imperix controllers feature 36 bidirectional 3.3V I/O lines, commonly known as USR pins. Driven directly from the FPGA, these custom-application I/Os are ideal for…

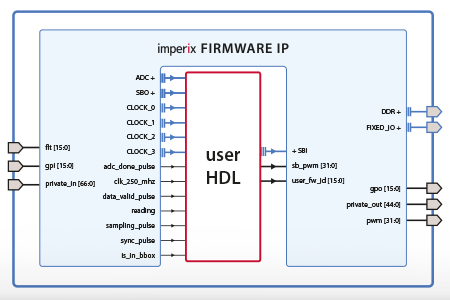

These pages give getting-started instructions and practical examples for customizing the FPGA firmware of the B-Box RCP or B-Board PRO. This allows offloading computations to the FPGA and developing specialized functions for very high-performance control algorithms.

Most imperix controllers feature 36 bidirectional 3.3V I/O lines, commonly known as USR pins. Driven directly from the FPGA, these custom-application I/Os are ideal for…

This page describes how to upgrade the imperix IP in an existing sandbox project, whether to restore compatibility with a newer SDK version or to…

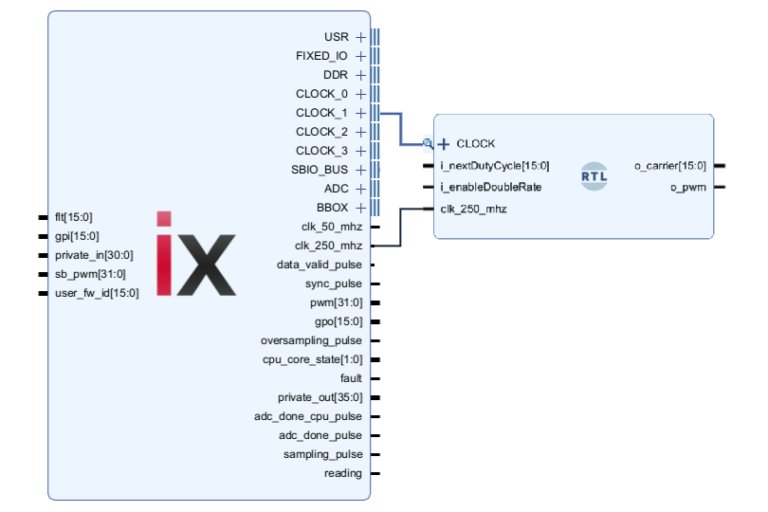

Beyond the built-in modulators accessible from the user application, the imperix sandbox enables PWM generation directly within the FPGA, allowing for the implementation of custom…

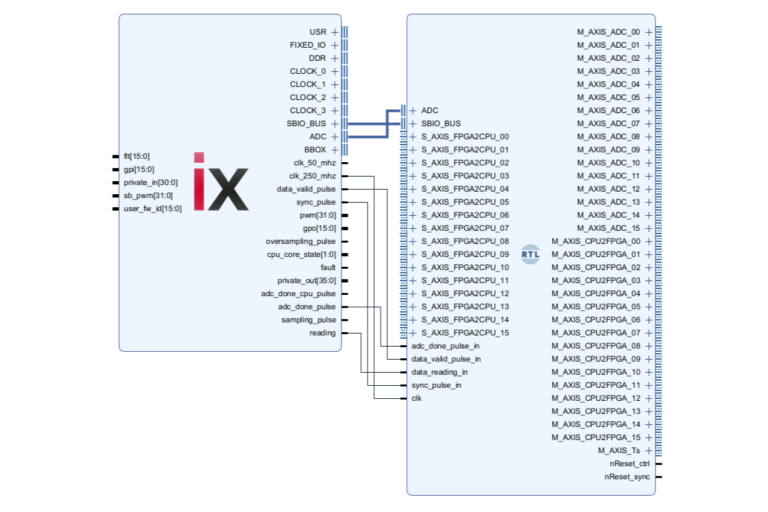

Imperix provides direct access to ADC measurements within the FPGA which allows for reduced delay between the sampling and the processing, but also helps supporting…

On imperix controllers, the CPU exchanges data with the FPGA via the SBIO bus. This memory-mapped bus allows the CPU user app to read and…

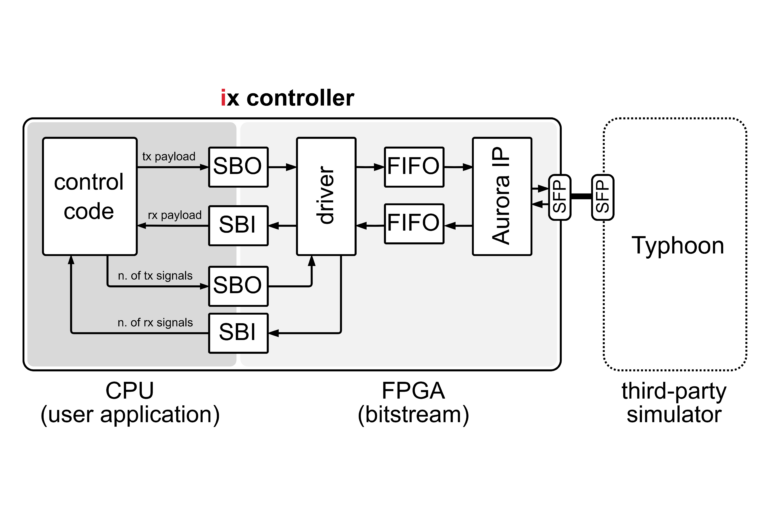

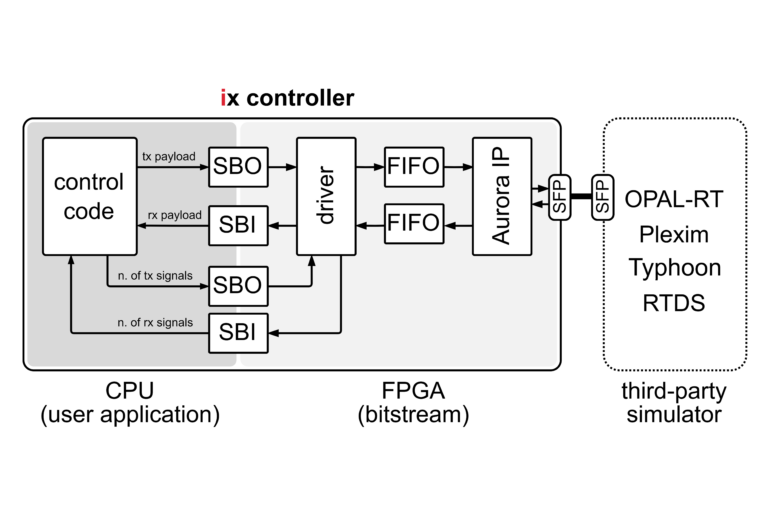

This page presents a practical example of Aurora communication with Typhoon HIL simulators, specifically the HIL101, HIL404, HIL506, and HIL606. It provides a ready-to-use user…

This note describes the control of an adapted Siemens SINAMICS S120 active line module using the imperix B-Board PRO embedded control platform. With its low…

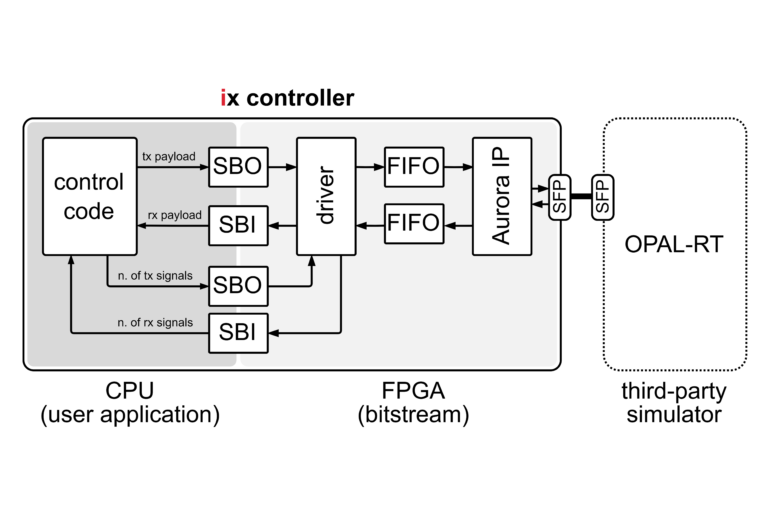

This page presents a practical example of Aurora communication with OPAL-RT simulators, specifically the OP4510 and OP4512. It provides a ready-to-use user application, along with…

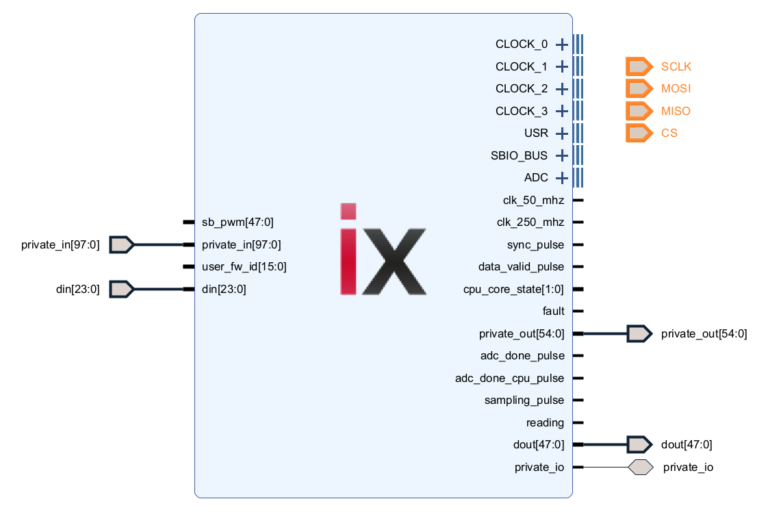

While imperix controllers are typically programmed with applications built in Simulink or PLECS, imperix also provides direct access to FPGA resources through its FPGA development…

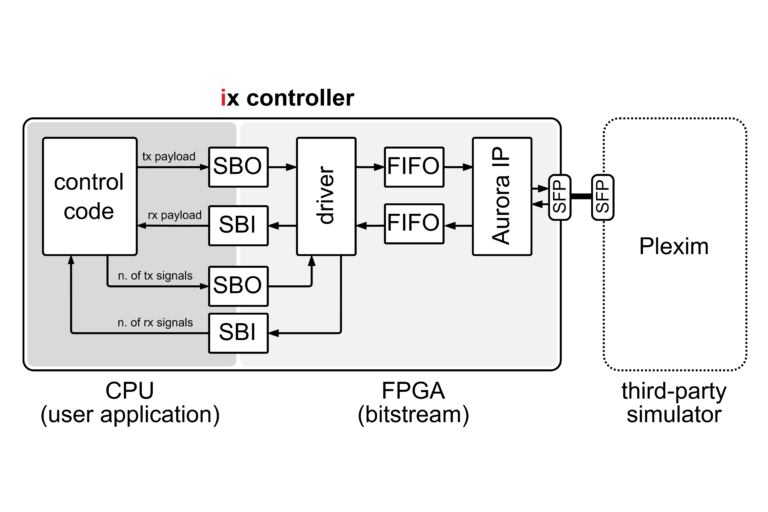

This page presents a practical example of Aurora communication with Plexim simulators, namely the RT-Box 1, RT-Box 2 and RT-Box 3. It provides a ready-to-use…

End of content

End of content