Table of Contents

The PEN block is a simulation model included in the Imperix Power library. It models the imperix NPC phase-leg PEN8018 in Simulink and PLECS simulation. For more information regarding how to get started with Imperix Power library, please read PN150.

This block also provides a thermal model for PEN8018. For more information regarding thermal simulation with the Imperix Power library, please read PN132.

• ACG SDK 2024.2: First release. Support for PLECS and Simulink SPS library (“Black” blocks).

• ACG SDK 2025.2: Addition of thermal models for most PEB and PEN modules.

• ACG SDK 2026.1: Support for the latest products (PEB-800-40, VSR-1000-ISO, VSR-500-HBW, CSR-25-HBW).

• ACG SDK 2026.1.3: Support for Simulink Simscape Electrical library (“Blue” blocks).

• Simulink (R2016a or newer): Simscape is required.

• Plexim PLECS (4.5 or newer): No particular requirement.

Additionally, for Simulink:

• Simscape Electrical library: Simscape Electrical is required.

• SPS library: Simscape Specialized Power Systems (up to R2025b) or OPAL-RT SPS Software is required.

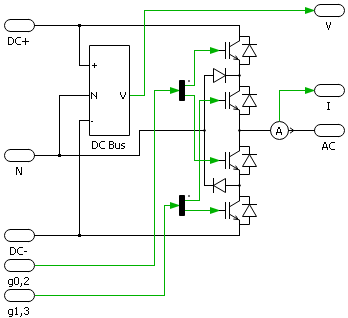

Electrical modeling of PEN

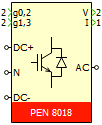

The schematic of the electrical model of PEN is depicted on the right. It has two modeling levels:

- (A) Simple

- (B) Detailed

For more detailed model parameters and measurement results, please contact [email protected].

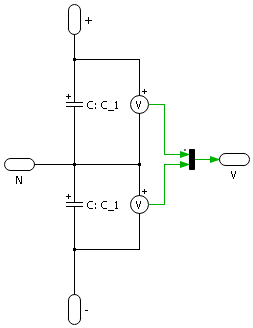

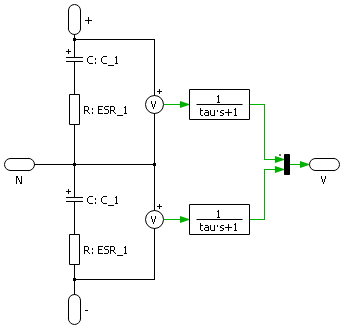

DC bus

The schematic of the equivalent DC bus is shown below.

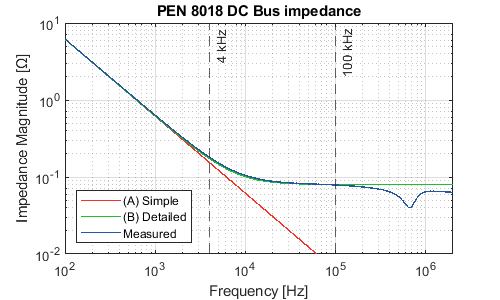

The simulation model is relevant within a given frequency range. The frequency validity range is 0-4 kHz for the (A) Simple level and 0-100 kHz for the (B) Detailed level. In that range, the impedance and transfer function of the model are reasonably close to the modeled system, which can be seen along with the plots of the proposed models. The model parameters are also displayed below.

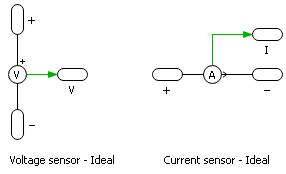

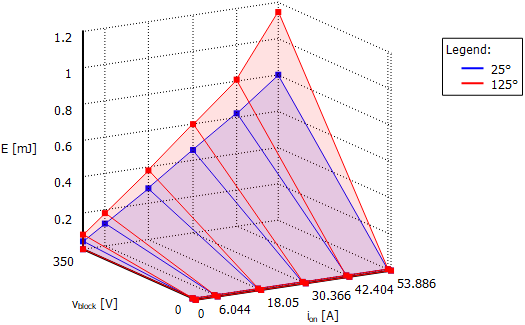

Embedded sensors

A generic sensor can be approximately modeled by an ideal sensor in series with an optional first-order Low-Pass Filter (LPF). The relationship between sensor’s bandwidth \(f_{BW}\) and the time constant \(\tau\) of the LPF follows \(\tau = \frac{1}{2\pi f_{BW}}\).

A sensor is modeled as a first-order LPF only if its bandwidth lies within the frequency range of a given modeling level. Otherwise, it is modeled as an ideal sensor. The following table summarizes the information on all the sensors in the PEN.

| Sensor | Bandwidth [kHz] | (A) Simple | (B) Detailed |

|---|---|---|---|

| PEN voltage sensor | 25 | Ideal | LPF |

| PEN current sensor | 450 | Ideal | Ideal |

Power transistors

The PEN block offers two options for modeling the power transistors:

- Switched The transistors are modeled by individual power semiconductors. The control inputs are instantaneous logical gate signals.

- Averaged The transistors are modeled by controlled voltage and current sources. The control inputs are the relative on-times of the semiconductors with values between 0 and 1. The gate signals can be either instantaneous (using only values 0 and 1) or time-averaged.

Although the functionality is practically the same, these options are named differently in PLECS and Simulink Simscape to be consistent with their naming conventions.

In Simulink Simscape only the Switched model is available, which is named:

- Switching devices

In PLECS they are named:

- Switched

- Sub-cycle average

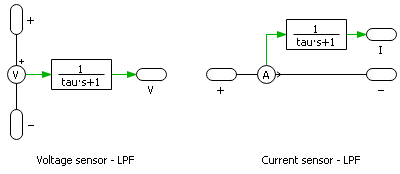

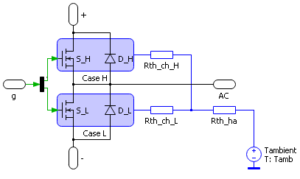

Thermal modeling of PEN

The schematic of the thermal model of PEN8018 is depicted on the right.

It includes the loss model of the semiconductors and the thermal impedance network between the junction and the ambient temperature.

Thermal impedance network

The thermal impedance model models only the thermal resistances, and all the thermal capacitances are either ignored or fixed at a small value to reduce the simulation time for the system to reach a thermal steady state. The model parameters are displayed below. Note that the thermal impedance between the junction and the case is included in the transistor’s thermal description file and thus is not present in the schematic.

| Thermal resistance | Value [K/W] |

| IGBT junction to case resistance | 1.49 |

| Diode junction to case resistance | 1.819 |

| Case to Heatsink resistance Rth_ch | 1.91 |

| Heatsink to ambient temperature resistance Rth_ha | 0.21 |

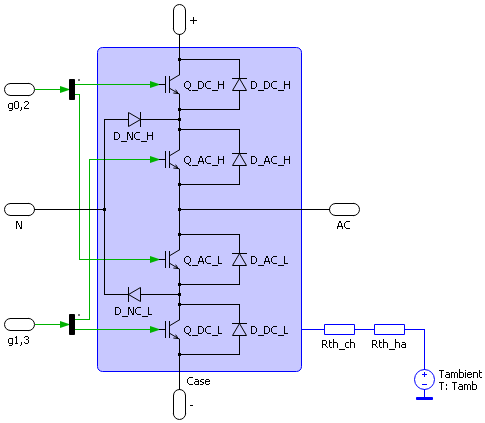

Semiconductor loss model

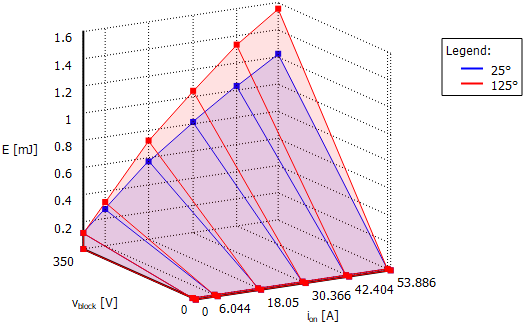

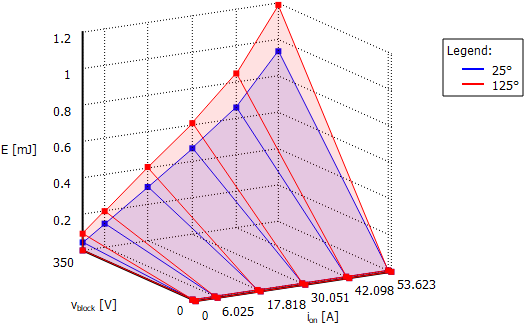

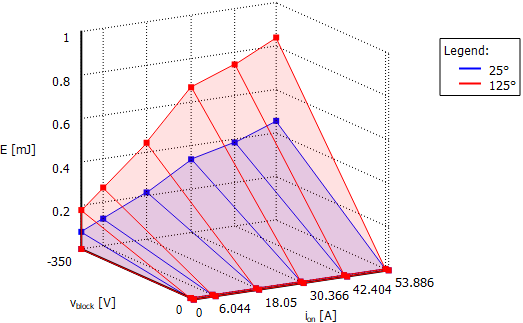

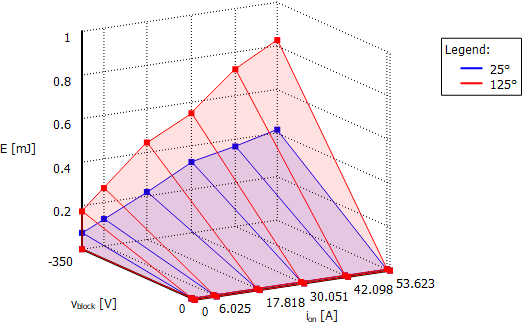

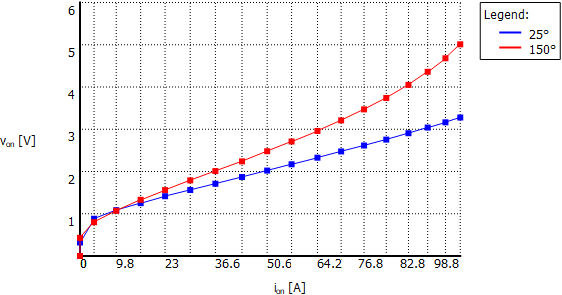

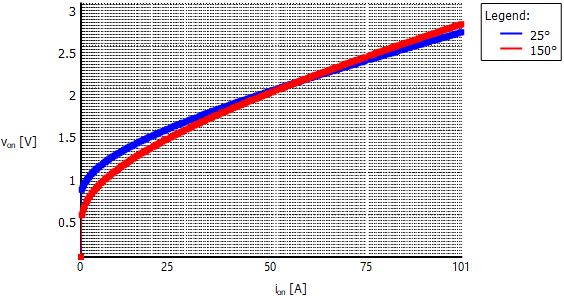

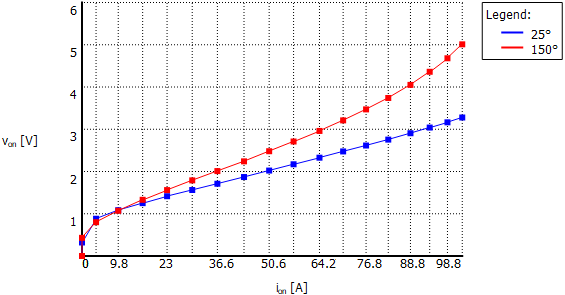

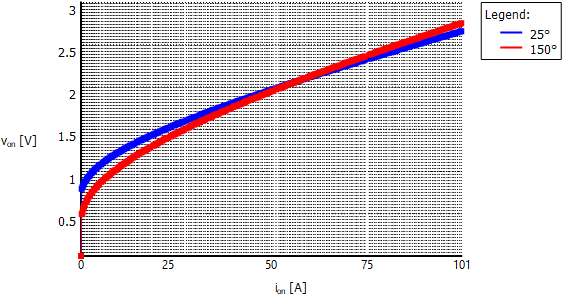

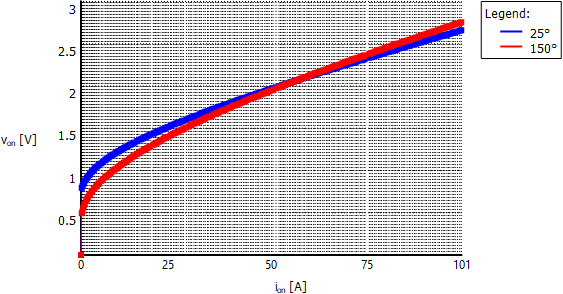

The semiconductor’s turn-on loss \(E_{on}\), turn-off loss \(E_{off}\), and on-state drain-to-source voltage \(V_{on}\) are modeled by look-up-tables provided by manufacturers. The module’s switching loss \(P_{sw}\) is calculated by periodic impulse averages of \(E_{on}\) and \(E_{off}\) over a chosen period, which is 1ms by default. The conduction loss \(P_{cond}\) is calculated by \(P_{cond} = V_{on} \cdot I_{on}\). The detailed model implementation in Simulink and PLECS can be viewed in PN132, and the look-up-tables are provided below.

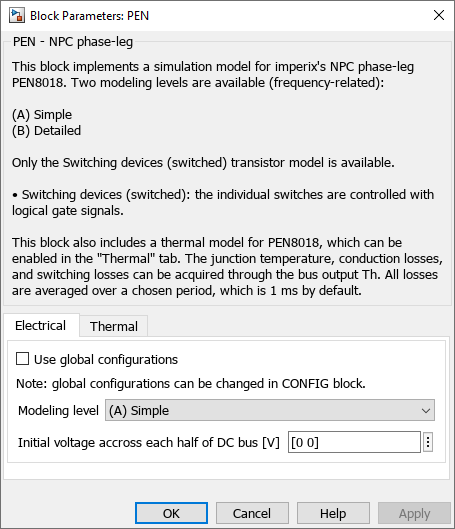

Simulink PEN block

Port specification

- The input

g0,2andg1,3are the gate signals. There are 4 signals in total, and the order is shown in the schematic.- For

Switching devices (switched)model,g0,2andg1,3are the 0/1 PWM signals. - For

Switching Function (averaged)model,g0,2andg1,3can be either the 0/1 PWM signal or the duty cycle between 0 and 1.

- For

- The output

Vis the measured voltages across each half of the DC bus. - The output

Iis the measured output current. - The output

This the thermal simulation results. This port is only visible when thermal simulation is enabled. - The connection port

DC+is the electrical port connected to the positive pole of the DC bus. - The connection port

DC-is the electrical port connected to the negative pole of the DC bus. - The connection port

Nis the electrical port connected to the midpoint of the DC bus. - The connection port

ACis the electrical port connected to the AC output.

Electrical parameters

Use global configurationsis ticked when the block receives global configurations from theConfigblock.Modeling levelselects the modeling level of the peripheral circuits.Initial voltage across each half of DC Bus [V]is a 2×1 array that defines the initial voltage across each half of the DC bus when the simulation starts.

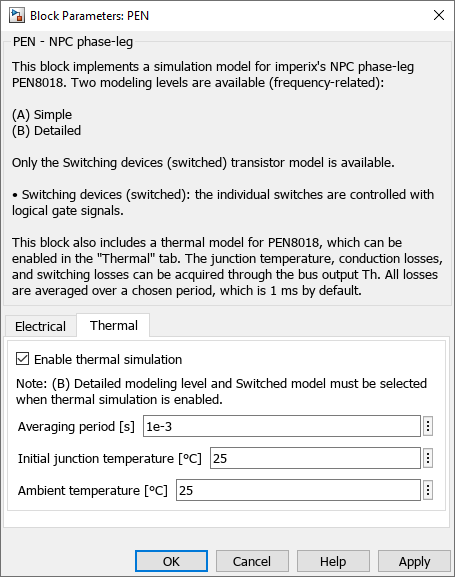

Thermal parameters

Enable thermal simulationis ticked when the thermal simulation is enabled.Averaging period [s]defines the averaging period for calculating switching loss.Initial junction temperature [°C]defines the initial junction temperature when the simulation starts.Ambient temperature [°C]defines the ambient temperature throughout the simulation.

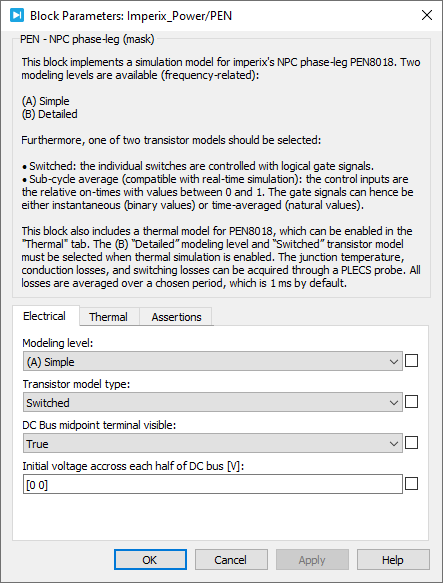

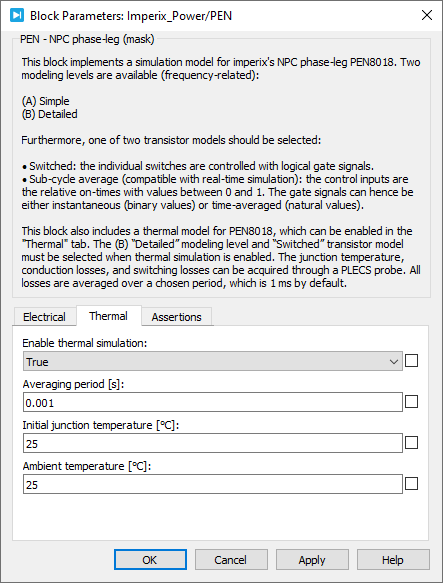

PLECS PEN block

Port specification

- The input

g0,2andg1,3are the gate signals. There are 4 signals in total, and the order is shown in the schematic.- For

Switchedmodel,g0,2andg1,3are the 0/1 PWM signals. - For

Sub-cycle averagemodel,g0,2andg1,3can be either the 0/1 PWM signals or the duty cycles between 0 and 1.

- For

- The output

Vis the measured voltages across each half of the DC bus. - The output

Iis the measured output current. - The connection port

DC+is the electrical port connected to the positive pole of the DC bus. - The connection port

DC-is the electrical port connected to the negative pole of the DC bus. - The connection port

Nis the electrical port connected to the midpoint of the DC bus. - The connection port

ACis the electrical port connected to the AC output.

Electrical parameters

Modeling levelselects the modeling level of the peripheral circuits.Transistor model typeselects the model of the power transistors.DC Bus midpoint terminal visibleshows or hides the portN.Initial voltage across each half of DC Bus [V]is a 2×1 array that defines the initial voltage across each half of the DC bus when the simulation starts.

Thermal parameters

Enable thermal simulationis ticked when the thermal simulation is enabled.Averaging period [s]defines the averaging period for calculating switching loss.Initial junction temperature [°C]defines the initial junction temperature when the simulation starts.Ambient temperature [°C]defines the ambient temperature throughout the simulation.

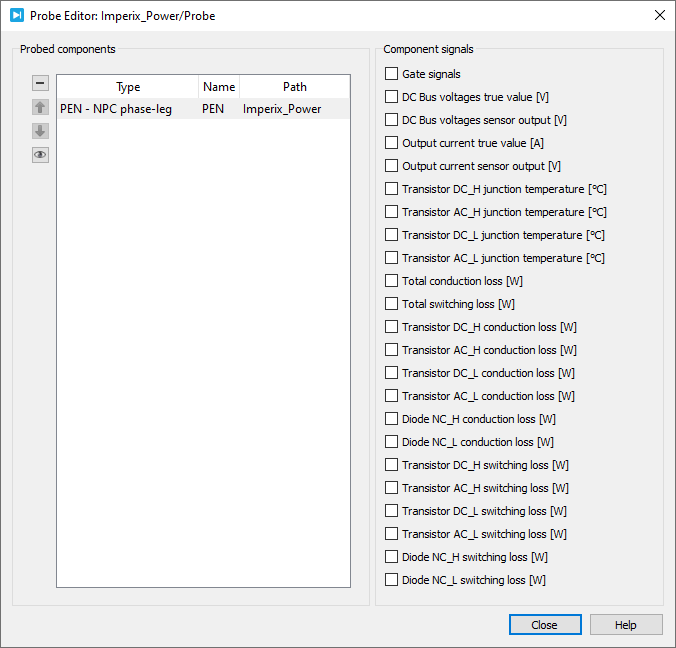

Probe signals

The following signals can be monitored by a Probe block in PLECS.

Gate signalsmonitors the gate signals present at the inputg.DC Bus voltages true value [V]monitors the true value of the DC bus voltages in Volt.DC Bus voltages sensor output [V]monitors the physical output of the DC bus voltage sensors in Volt.Output current true value [A]monitors the true value of the output current in Amp.Output current sensor output [V]monitors the physical output of the output current sensor in Volt.

The following signals contain thermal simulation results that can be monitored when thermal simulation is enabled.

Transistor DC_H junction temperature [°C]monitors the junction temperature of transistor DC_H in °C.Transistor AC_H junction temperature [°C]monitors the junction temperature of transistor AC_H in °C.Transistor DC_L junction temperature [°C]monitors the junction temperature of transistor DC_L in °C.Transistor AC_L junction temperature [°C]monitors the junction temperature of transistor AC_L in °C.Total conduction loss [W]monitors the module’s total conduction loss in Watt.Total switching loss [W]monitors the module’s total switching loss in Watt.Transistor DC_H conduction loss [W]monitors the conduction loss of transistor DC_H in Watt.Transistor AC_H conduction loss [W]monitors the conduction loss of transistor AC_H in Watt.Transistor DC_L conduction loss [W]monitors the conduction loss of transistor DC_L in Watt.Transistor AC_L conduction loss [W]monitors the conduction loss of transistor AC_L in Watt.Diode NC_H conduction loss [W]monitors the conduction loss of diode NC_H in Watt.Diode NC_L conduction loss [W]monitors the conduction loss of diode NC_L in Watt.Transistor DC_H switching loss [W]monitors the switching loss of transistor DC_H in Watt.Transistor AC_H switching loss [W]monitors the switching loss of transistor AC_H in Watt.Transistor DC_L switching loss [W]monitors the switching loss of transistor DC_L in Watt.Transistor AC_L switching loss [W]monitors the switching loss of transistor AC_L in Watt.Diode NC_H switching loss [W]monitors the switching loss of diode NC_H in Watt.Diode NC_L switching loss [W]monitors the switching loss of diode NC_L in Watt.