Table of Contents

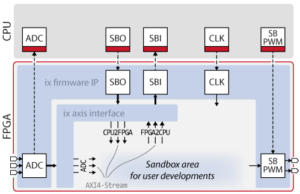

The Sandbox Input from FPGA (SBI) block reads the value of the SBI registers in the FPGA. It is used to transfer data from user-made code within the FPGA to the CPU. To transfer data from the CPU to the user-made code within the FPGA, the SBO block should be used.

Information on FPGA edition is available on:

Usage examples of the SBI block are available on:

- FPGA-based hysteresis current control (TN120)

- FPGA-based SPI communication IP for A/D converter (TN130)

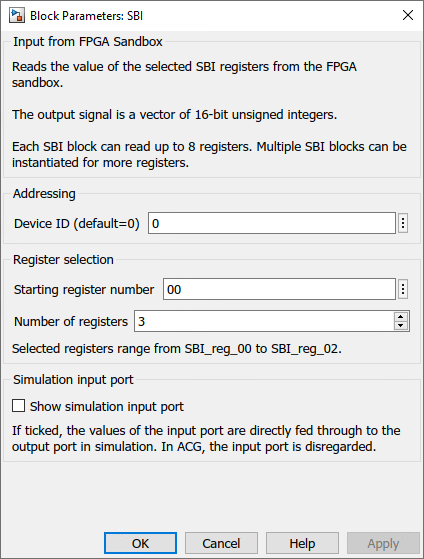

Simulink block

Signal specification

The output returns a vector of the 16-bit unsigned integers representing the SBI register values. Up to 8 registers can be read from a single SBI block. Multiple SBI blocks can be used to read more registers.

Parameters

Device IDselects which B-Box/B-Board to address when used in a multi-device configuration.Starting register numberandNumber of registersdefines the range of registers to read.

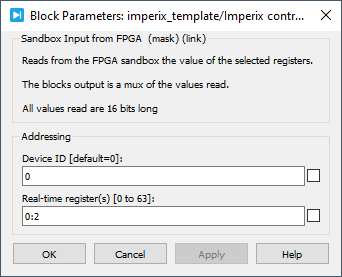

PLECS block

Signal specification

The output returns a vector of the 16-bit unsigned integers representing the SBI register values. Up to 8 registers can be read from a single SBI block. Multiple SBI blocks can be used to read more registers.

Parameters

Device IDselects which B-Box/B-Board to address when used in a multi-device configuration.Starting register numberandNumber of registersdefines the range of registers to read.