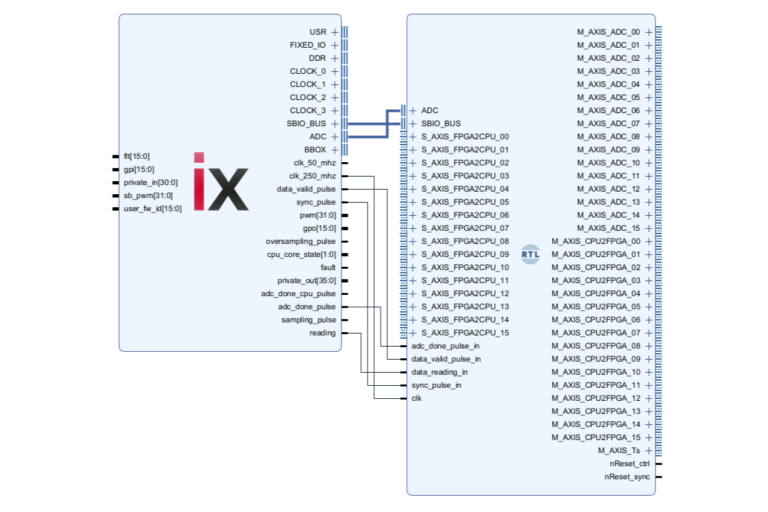

Retrieving ADC measurements from the FPGA

Imperix provides direct access to ADC measurements within the FPGA which allows for reduced delay between the sampling and the processing, but also helps supporting…

Imperix provides direct access to ADC measurements within the FPGA which allows for reduced delay between the sampling and the processing, but also helps supporting…

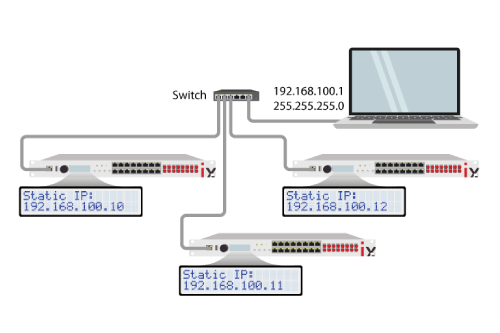

In most cases, connecting to the target using its dynamic IP address is straightforward and requires no additional setup. This dynamic IP is typically either…

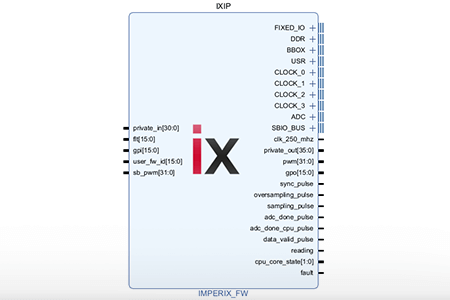

This page provides the imperix sources files required to start programming the FPGA on imperix controllers. The provided archive contains the imperix firmware IP and…

The B-Box RCP SD card contains the B-Box firmware (bitstream.bit.bin and linux.bin) and the license file (license.lic). Other optional files may also be present on…

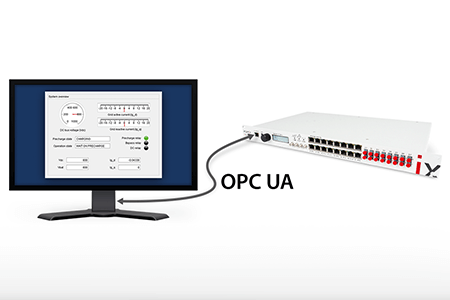

The Industrial Communication Toolbox Add-On for MATLAB and Simulink (formerly OPC Toolbox) allows communicating with an OPC UA server directly from MATLAB. This page explains…

Imperix relies on the increasingly popular OPC UA industrial protocol to interact with programmable controllers remotely. To do so, imperix controllers (or the TPI8032) embed…

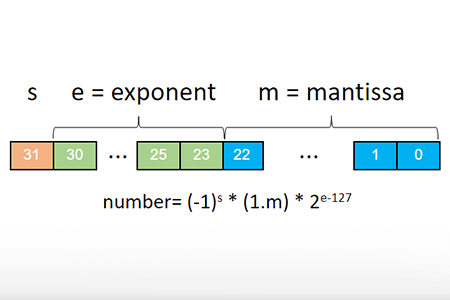

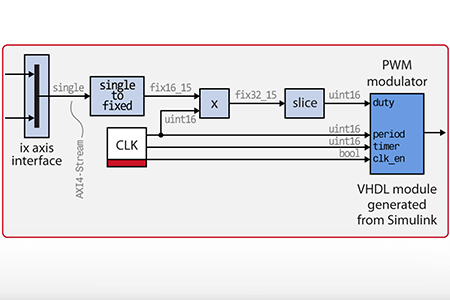

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

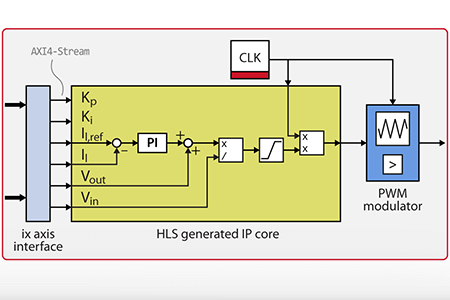

High-level synthesis (HLS) tools greatly facilitate the implementation of complex power electronics controller algorithms in FPGA. Indeed HLS tools allow the user to work at…

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents…

End of content

End of content