Installing the Xilinx Blockset for Simulink

The Xilinx blockset for MATLAB & Simulink is a single toolbox that unifies Model Composer (HLS), System Generator for DSP (HDL) as well as the Xilinx AI…

The Xilinx blockset for MATLAB & Simulink is a single toolbox that unifies Model Composer (HLS), System Generator for DSP (HDL) as well as the Xilinx AI…

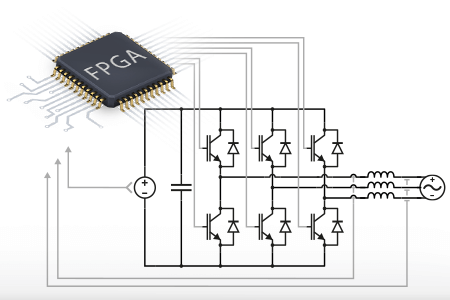

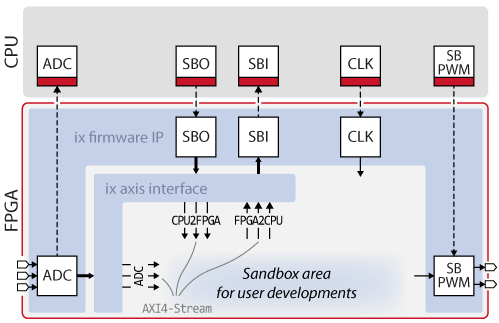

Usually, the user programs the imperix controller’s CPU using imperix ACG SDK or C++ SDK, and uses the pre-implemented FPGA peripherals such as the ADC…

While the standard imperix workflow utilises the ACG SDK (for Simulink or PLECS ) or the CPP SDK (for C/C++) to program the controller’s CPU,…

Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the…

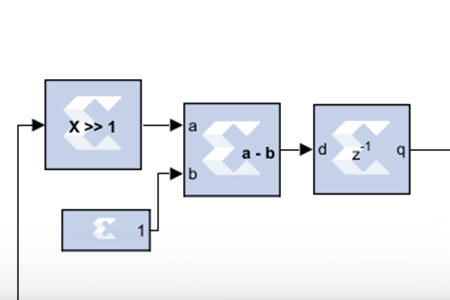

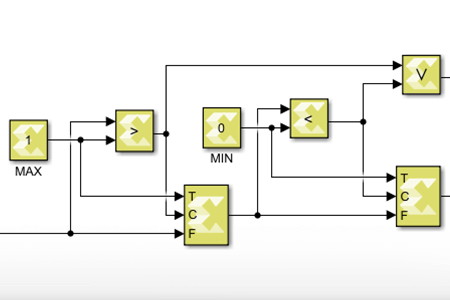

Xilinx System Generator for DSP (SysGen) is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical blocks programming. Users can…

Model Composer is a Simulink add-on software developed by Xilinx. It is a high-level synthesis (HLS) tool that allows the user to program an FPGA-based…

The tunable parameter block creates a variable that can be altered in real-time using imperix Cockpit. It supports the int32, uint32, and float data types. Simultaneously, the tunable parameter…

The probe variable block creates a variable that can be watched and logged in real-time using using imperix Cockpit. It supports the int32, uint32, and…

The Core state block returns the state of the target: The block also provides a second signal called “reset” that can be wired to the…

The external reset block provides a signal that can be wired to the external reset input of PID controllers to keep the integrator at reset…

End of content

End of content