Accessing the USR pins in the FPGA sandbox

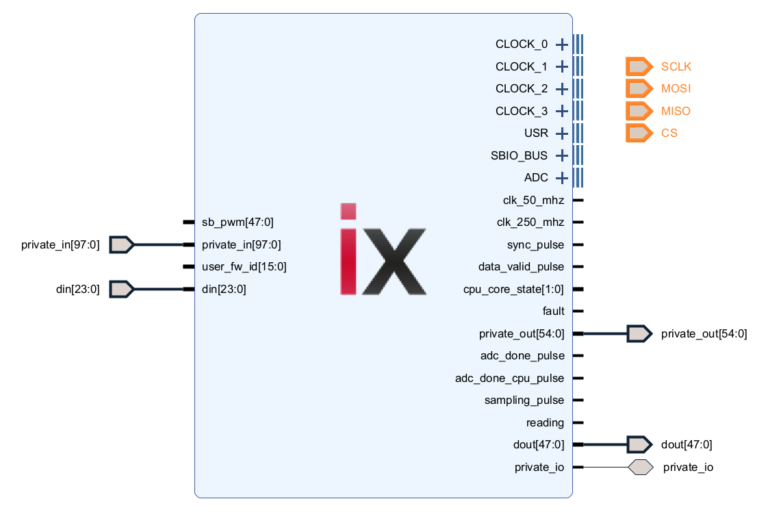

Most imperix controllers feature 36 bidirectional 3.3V I/O lines, commonly known as USR pins. Driven directly from the FPGA, these custom-application I/Os are ideal for…

These notes are specifically related to imperix products. They address both control or power hardware, as well as software solutions. Their aim is to document what users should understand to properly use imperix products. Product notes, therefore, provide complementary information with respect notably to product datasheets.

Most imperix controllers feature 36 bidirectional 3.3V I/O lines, commonly known as USR pins. Driven directly from the FPGA, these custom-application I/Os are ideal for…

This page describes how to upgrade the imperix IP in an existing sandbox project, whether to restore compatibility with a newer SDK version or to…

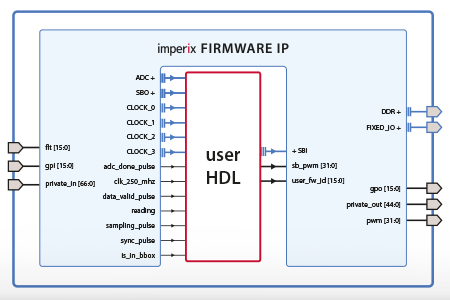

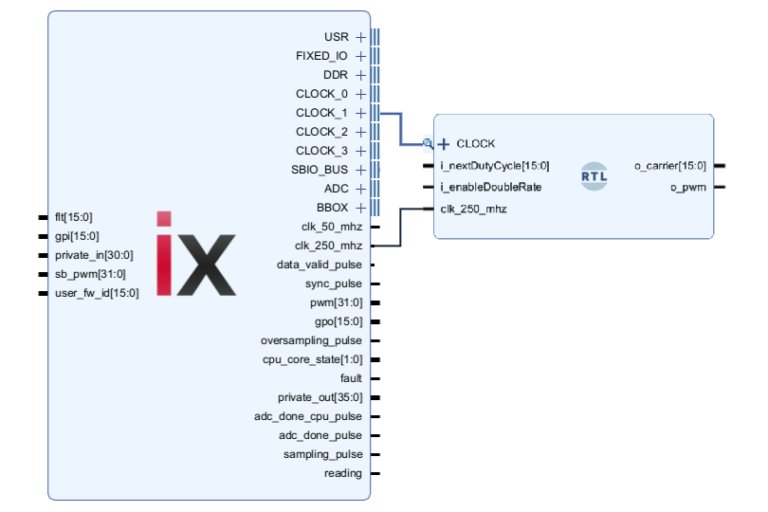

Beyond the built-in modulators accessible from the user application, the imperix sandbox enables PWM generation directly within the FPGA, allowing for the implementation of custom…

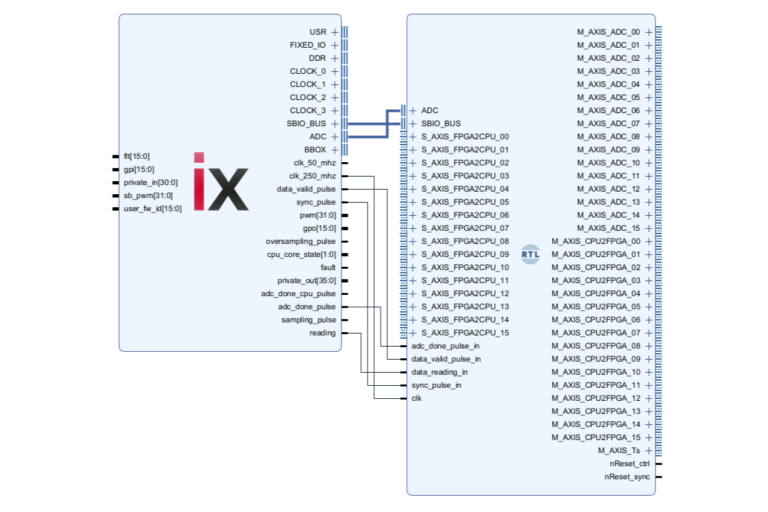

Imperix provides direct access to ADC measurements within the FPGA which allows for reduced delay between the sampling and the processing, but also helps supporting…

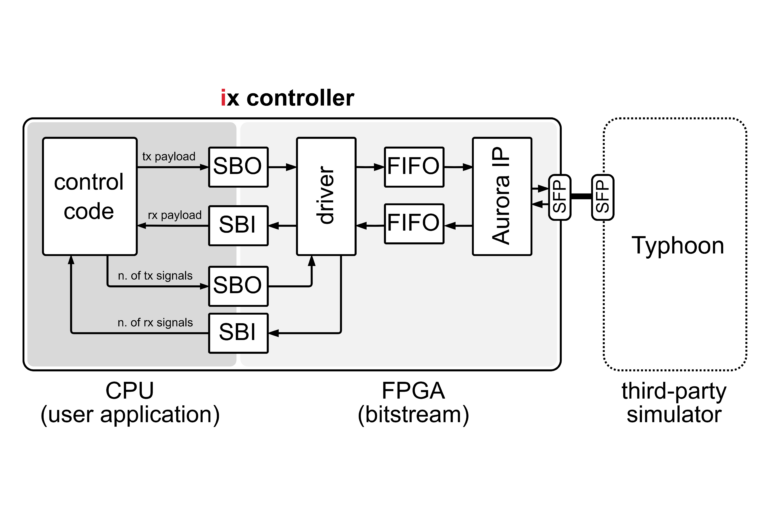

On imperix controllers, the CPU exchanges data with the FPGA via the SBIO bus. This memory-mapped bus allows the CPU user app to read and…

This page presents a practical example of Aurora communication with Typhoon HIL simulators, specifically the HIL101, HIL404, HIL506, and HIL606. It provides a ready-to-use user…

This page outlines the configuration methods for analog I/O channels on imperix controllers. While digital I/Os are configured exclusively via software and remain consistent across…

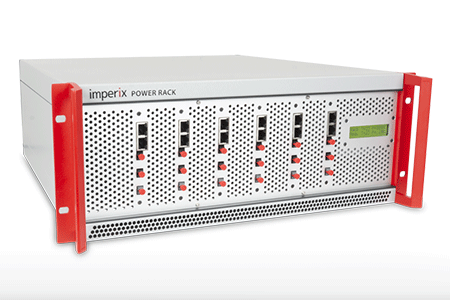

This document introduces the two variants of the closed rack (types C and D). Intended for first-time users, the guide details the auxiliary power supply…

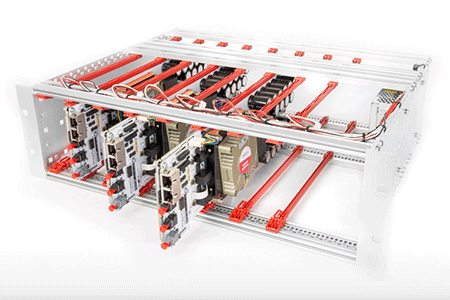

This document provides guidance for integrating imperix power modules into an open rack (type A). Intended for first-time users, the guide details essential mechanical considerations,…

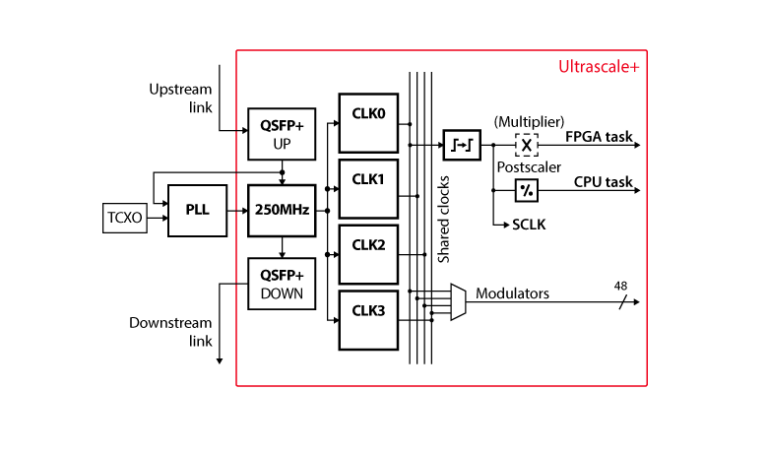

This article details the underlying clock architecture and timing configurations of imperix controllers, focusing on the four internal time bases (CLK0–CLK3) that govern ADC sampling,…

End of content

End of content