Timing configuration on imperix controllers

This article details the underlying clock architecture and timing configurations of imperix controllers, focusing on the four internal time bases (CLK0–CLK3) that govern ADC sampling,…

This article details the underlying clock architecture and timing configurations of imperix controllers, focusing on the four internal time bases (CLK0–CLK3) that govern ADC sampling,…

Introduction Power electronic converters pose a specific sampling challenge: the signals of interest (currents and voltages) are low-frequency components, but they are combined with a…

This technical note provides an overview of Active Power Filters (APFs) designed for harmonic mitigation and specifically targeting three-phase grid-connected inverters. The note begins by…

This technical note presents a selection of the most prevalent grid synchronization methodologies employed in grid-tied power converters. These methods are crucial for enabling power…

This note provides insights into the operating principle of a synchronous reference frame PLL (SRF PLL), also known as DQ-type PLL. An implementation of an…

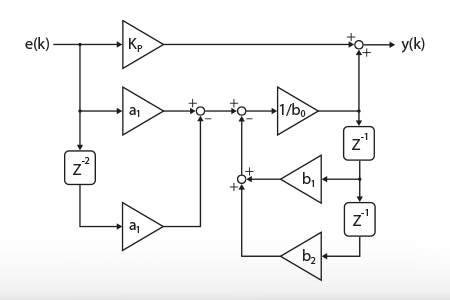

A proportional resonant control can be seen as the implementation of PI controllers within a rotating reference frame (dq), which allows to re-locate the infinite DC gain at desired frequency.

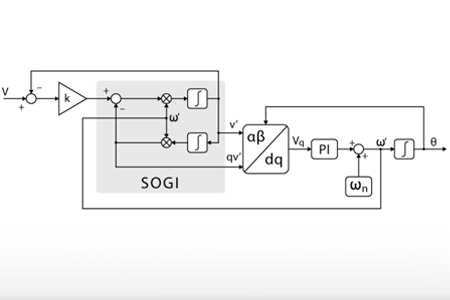

Second-order Generalized Integrators (SOGI) have recently been proposed for use as phase detectors for PLL implementations. These structures are essentially notch filters (band-pass) that can be easily tuned to the grid frequency.

End of content

End of content