Using an ILA to debug an FPGA designF

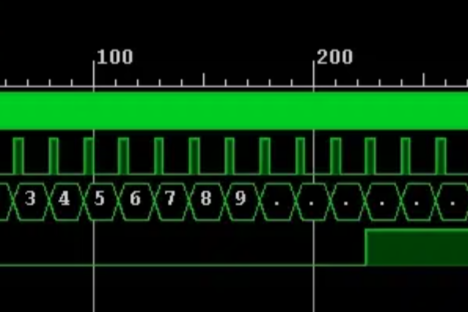

Debugging an FPGA design can be difficult without clear visibility into the high-speed logic fabric, where signals change at nanosecond scales. Xilinx Integrated Logic Analyzer…

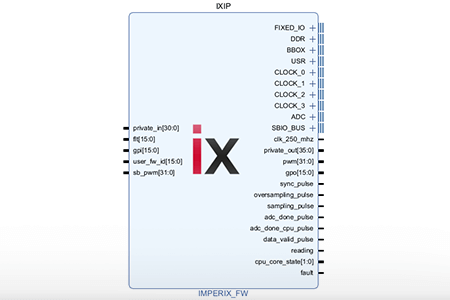

These pages give getting-started instructions and practical examples for customizing the FPGA firmware of the B-Box RCP or B-Board PRO. This allows offloading computations to the FPGA and developing specialized functions for very high-performance control algorithms.

Debugging an FPGA design can be difficult without clear visibility into the high-speed logic fabric, where signals change at nanosecond scales. Xilinx Integrated Logic Analyzer…

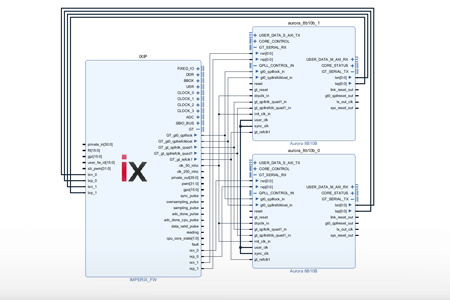

The SFP ports on imperix controllers are typically used for interconnecting devices in a RealSync network. However, when customizing the FPGA firmware, imperix designed the…

This page provides the imperix sources files required to start programming the FPGA on imperix controllers. The provided archive contains the imperix firmware IP and…

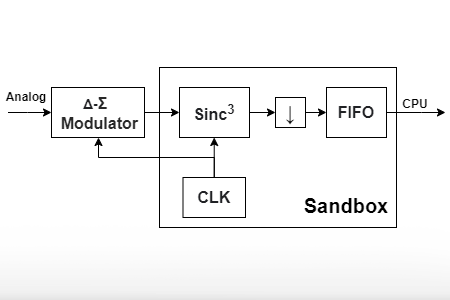

This technical note shows how to build a decoder IP for a Delta-Sigma Modulator and establish communication with such a device through USR ports of…

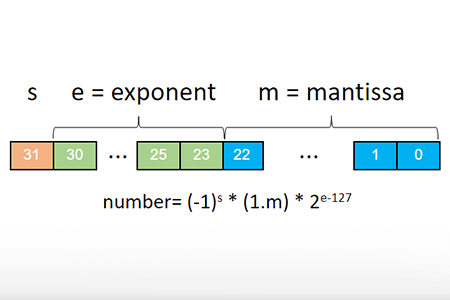

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

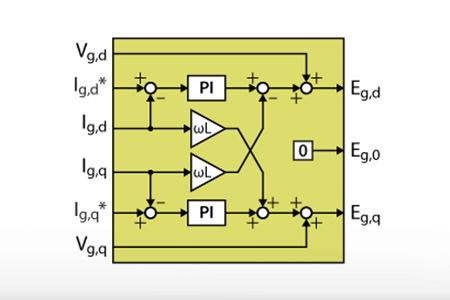

Control algorithms for power electronics converters often rely on PI controllers executed on the CPU of the controller. That’s the technique used in most of…

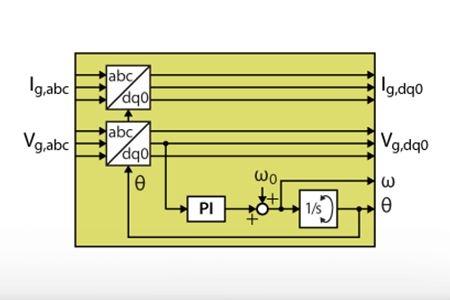

The operation of a grid-tied power converter (such as the 3-phases PV inverter) requires that the control software implements a grid synchronization technique. One well-known…

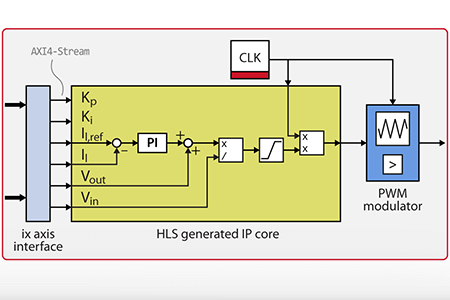

High-level synthesis (HLS) tools greatly facilitate the implementation of complex power electronics controller algorithms in FPGA. Indeed HLS tools allow the user to work at…

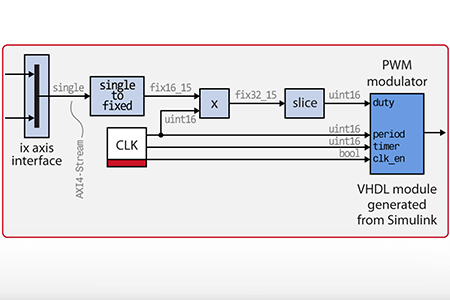

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents…

End of content

End of content