Table of Contents

The CONFIG block primarily serves to configure the main clock (CLK0) as well as its derivatives. Together, these clocks define the frequency and phase of the sampling events as well as the timing of the CPU interrupt (triggering the execution of the control task). CLK0 being indispensable to the proper operation of the hardware, so is the CONFIG block.

Secondary configuration options are also appended to the CONFIG block, such as:

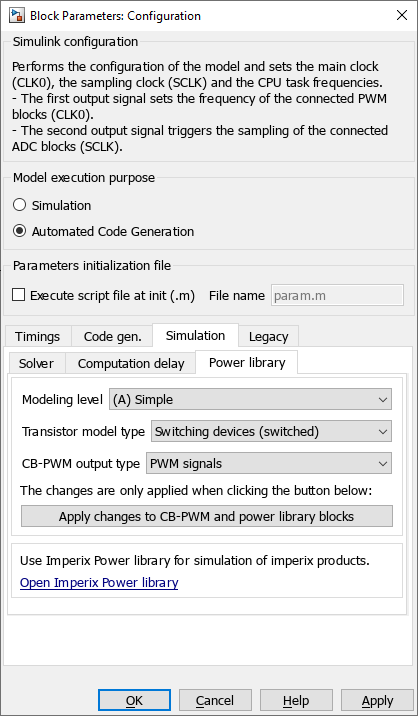

- The model execution purpose (Simulink only) – See PN134.

- The target hardware generation (Simulink only) – See PN134.

- Solver parameters – See below.

- Plant-side modeling options – See PN150.

The CONFIG block is available for all imperix controllers, on which it behaves identically.

Key principles of operation

Imperix controllers offer four configurable times bases, configurable using the CLK0-CLK3 signals. CLK0 deserves particular attention as it is always active and statically associated to the sampling and control tasks. CLK0 is also limited to a constant frequency, thereby imposing regular sampling. CLK1-CLK3 are optional signals, which can be of variable frequency and freely associated to different modulators (see CLK block).

Several clocks are derived from CLK0, the two most important of which are:

- The physical sampling base clock SCLK, of frequency FSCLK. It only differs from CLK0 by a configurable sampling phase (constant).

- The CPU interrupt, responsible for launching the control task, of frequency FCPU. If needed, FCPU can be defined as a decimated derivative of FSCLK using a post-scaling coefficient.

Typical timing configurations

With imperix controllers, the timing configuration for the sampling, control and modulation is essentially made by adequately wiring the corresponding blocks to the four time bases (i.e. CLK0-CLK3). The following configurations are notably possible:

- Single-rate sampling, in which case the control task is executed once per PWM period. Sampling, control and modulation are all linked to CLK0, with adequate phase-shifts. This case is the default configuration implemented in most examples.

- Double-rate sampling, in which case the control task is executed twice per PWM period. Sampling and control are linked to CLK0 (with adequate phase-shift), whereas modulation must be linked to another clock (e.g. CLK1), configured at half the frequency of CLK0. This case gives best performance, provided that sufficient CPU time is available.

- Advanced sampling configurations are also possible, typically authorizing to retrieve multiple samples at once (data history), variable-frequency switching, or running FPGA-based control tasks at a higher rate than the CPU.

Inside Simulink/PLECS, the two clocks available as outputs of the CONFIG block can be easily used for implementing the above-described scenarios. In practice, they serve the two following purposes:

- In simulation mode, the sampling clock SCLK is indispensable to properly account for the exact sampling instant within the simulation model. This is also essential to properly model the discrete nature of the control’s execution. Similarly, the CLK0 output is also important to take into account the relative phase of the modulation with respect to the sampling, as well as potential phase-shifts between modulators.

- In code generation mode, these signals do not infer any software variable, but are analyzed by Simulink/PLECS as to properly map the connected resources to the physical hardware clocks.

More details regarding how Simulink and PLECS handle thes ascpects are presented in PN135 (Simulink) and PN137 (PLECS).

Block parameters

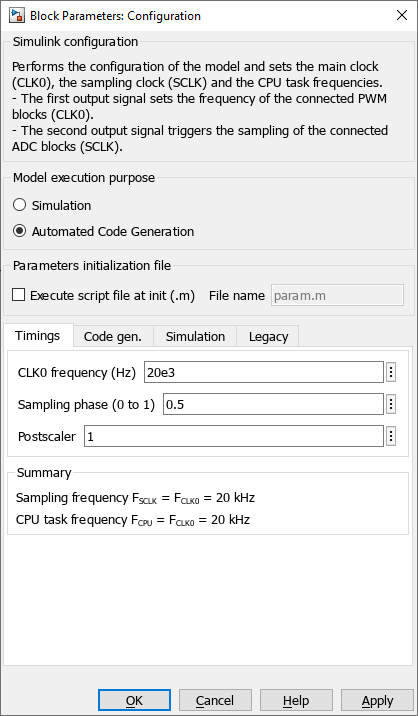

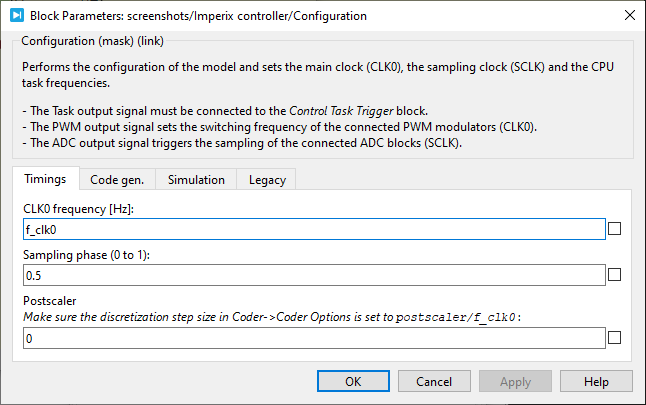

Timings

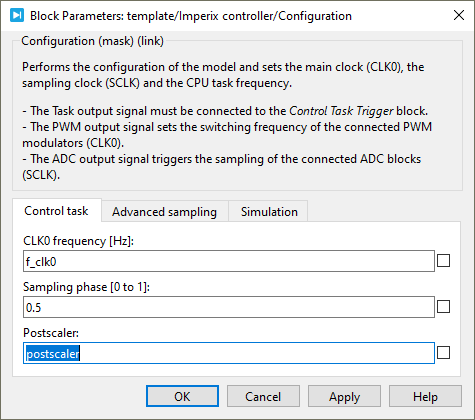

- The CLK0 frequency sets the main clock frequency FCLK0, which provides the time base for generating the ADC sampling strobe SCLK.

- The sampling phase sets the phase-shift of the ADC sampling strobe SCLK relative to CLK0. The CPU control task is executed immediately once the values are available. If the modulators are also tied to CLK0, equivalences exist between phase-shifting the sampling or the modulation.

- The postscaler is used to decimate the CPU task execution rate relatively to SCLK such that

FCPU = FCLK0 /postscaler.

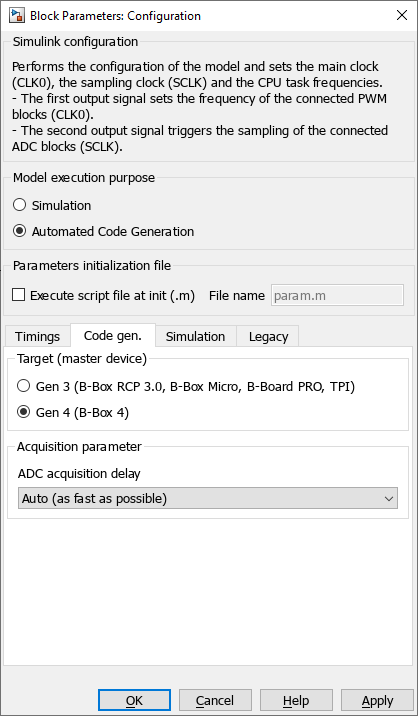

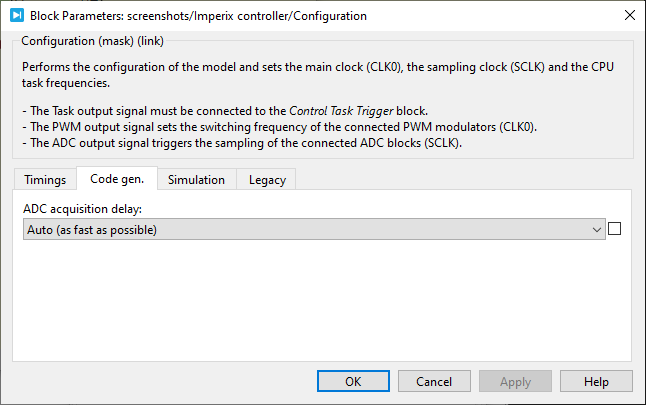

Code generation

- The Target is a Simulink-specific parameter that defines which hardware the code will be generated for. In PLECS, the equivalent parameter is located in Coder -> Coder option… (Ctrl+Alt+B). The two possible options are:

- Gen 3 (B-Box RCP3.0, B-Box Micro, B-Board PRO, TPI)

- Gen 4 (B-Box 4 only)

- The ADC acquisition delay corresponds to complete conversion time, counted from the ADC sampling instant (identical for all channels) to the availability of the data in the CPU cache, right before the execution of the control task. This parameter can take multiples values amongst imperix controllers. The available options are:

- Auto (as fast as possible, recommended) – This automatically selects the fastest possible option. This is identified at launch time, as slaves may be connected to the target.

- 2 μs (all devices) – This conservative legacy setting is available for all controllers.

- 500 ns (all devices except B-Box RCP 3.0) – This setting is available for all controllers except B-Box 3.

- 200/368 ns (B-Box 4 only) – This high-performance setting is only available on B-Box 4.

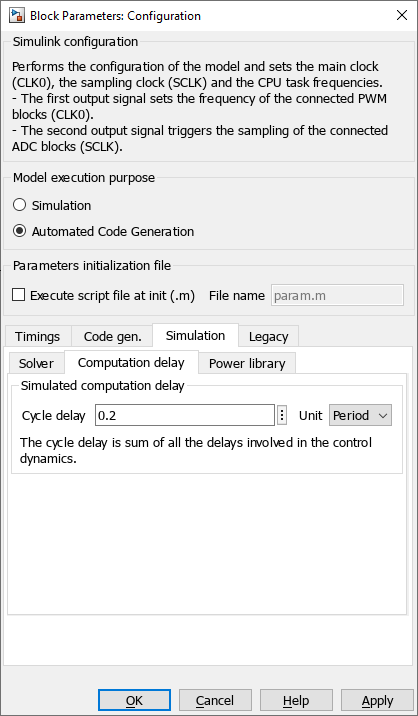

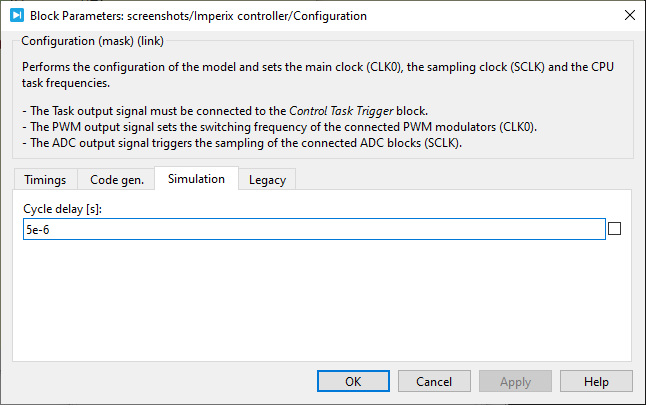

Simulation

- Basic Solver parameters can be directly set in the associated tab. These are coming from the “Model Configuration Parameters” (Ctrl+E), with which they are automatically synchronized. These solver parameters only apply to the variable-step solver used in simulation mode.

- The Computation delay is exclusively used in simulation mode. It serves to accurately model the total time required for computing the control task, impacting the moment at which the PWM parameters are actually updated. As such, it sums up the delays involved in the control dynamics (ADC acquisition, data read, control task execution, data write).

As the cycle delay cannot be known before the control code is actually run on the target, this parameter must be measured during run time and adjusted accordingly. To this end, the Cockpit timings tab provides the necessary information. - The Power library parameters are documented in the Getting started with Imperix Power library page.

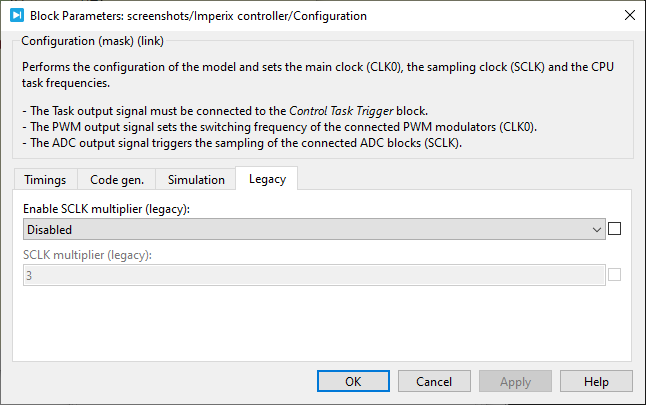

Legacy parameters

- The SCLK multiplier parameter (previously called oversampling) allows setting a multiplier such that FSCLK = FCLK0 x

multiplier. This parameter is maintained for legacy reasons. To obtain a sampling frequency higher than the CPU execution frequency, it is rather recommended to increase FCLK0 and use the postscaler.

Simulink block

Signal specification

The behavior of these signals during simulations is described in Simulation essentials with Simulink (PN135).

Mask

PLECS block

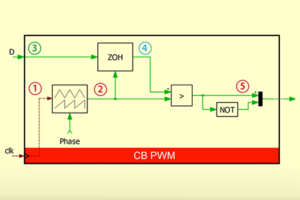

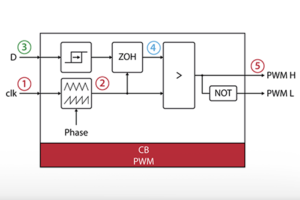

- The

Taskoutput must be connected to the Control Task Trigger block. The Control Task Triggernominal base sample timemust be equal topostscaler/CLOCK_0frequency. - The

PWMclock signal must be connected to the>input of the PWM blocks to set their frequency to the CLK0 frequency. - The

ADCclock output is the sampling signal SCLK. It must be connected to the>input signal of all the ADC blocks.

The behavior of these signals during simulations is described in Simulation essentials with PLECS (PN137)

Mask

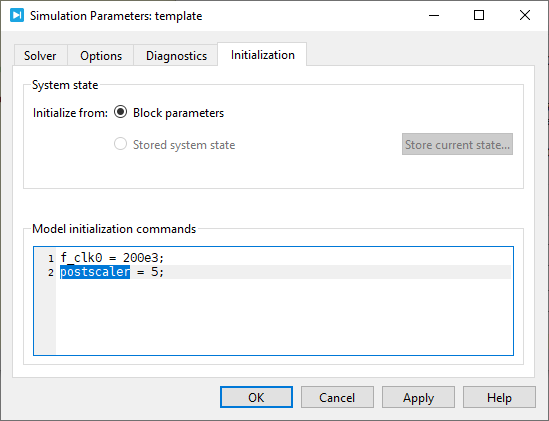

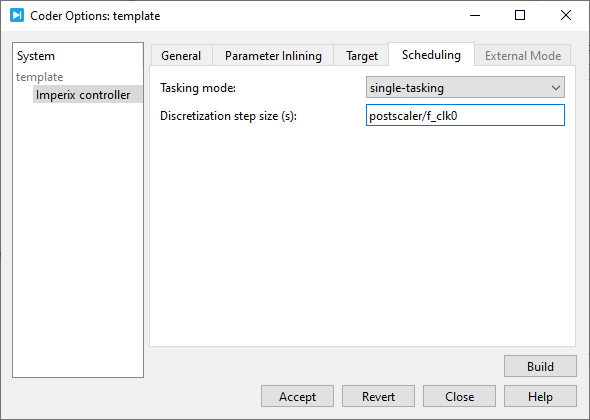

Changing the postscaler in PLECS

In PLECS, the discretization step size must match the CPU control task period for the generated code to behavior properly. When using the postscaler, the discretization step size must be set to postscaler/FCLK0. A simulation variable can be used for convenience, as illustrated below: