PP-PWM – Programmed Patterns PWM

The FPGA-based PP-PWM (programmed pulse pattern) peripheral provides a specialized PWM scheme for two and three-level inverters, which relies on pre-computed pulse patterns. This type…

The FPGA-based PP-PWM (programmed pulse pattern) peripheral provides a specialized PWM scheme for two and three-level inverters, which relies on pre-computed pulse patterns. This type…

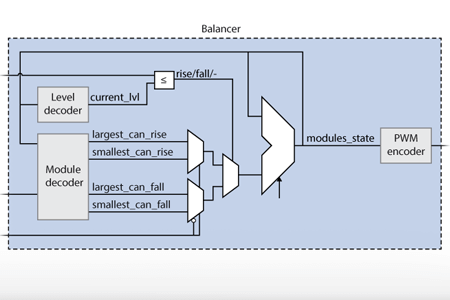

The SS-PWM peripheral provides a specialized Pulse Width Modulation scheme (PWM) for multilevel converters, which directly integrates means for balancing series-connected submodules. Such an approach…

This technical note offers insights into the SS-PWM peripheral block, which is part of the standard firmware of imperix controllers. The SS-PWM block provides multilevel…

The “dq0 to Alpha-Beta-Zero” converts a space vector from a rotating (dq0) to a stationary (αβ0) reference frame. The angle of the rotating reference frame…

The “Alpha-Beta-Zero to dq0” block converts a space vector from a stationary (αβ0) to a rotating reference frame (dq0). The angle of the rotating reference…

The “Alpha-Beta-Zero to abc” block computes a three-phase (abc) signal from a space vector in a stationary reference frame (αβ0). The transformation is performed using…

The “adc to Alpha-Beta-Zero” block computes the coordinates of a three-phase (abc) signal in a stationary reference frame (αβ0). The transformation is performed using the…

The “dq0 to abc” block computes a three-phase (abc) signal from a space vector in a rotating reference frame (dq0). The angle of the rotating…

The “abc to dq0” block computes the coordinates of a three-phase (abc) signal in a rotating reference frame (dq0). The angle of the rotating reference…

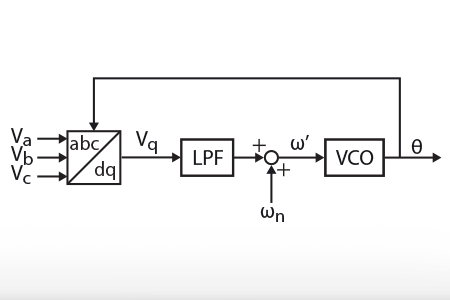

This note provides insights into the operating principle of a synchronous reference frame PLL (SRF PLL), also known as DQ-type PLL. An implementation of an…

End of content

End of content