FPGA implementation of a PLL for grid synchronization

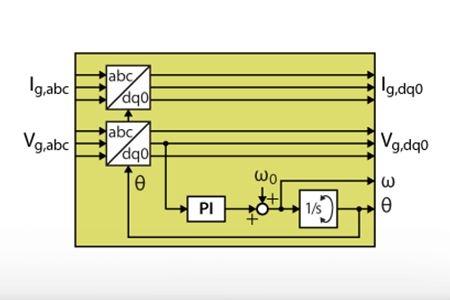

The operation of a grid-tied power converter (such as the 3-phases PV inverter) requires that the control software implements a grid synchronization technique. One well-known approach consists in using a three-phase PLL to project the AC grid quantities into a synchronous rotating reference frame. The PLL algorithm is usually executed on the CPU of the…