AMD Xilinx Vivado Design Suite installation

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

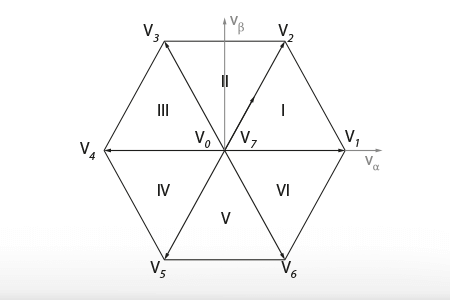

What is the space vector modulation (SVM) technique and how does it work? To answer these questions, this article introduces first the notions of active…

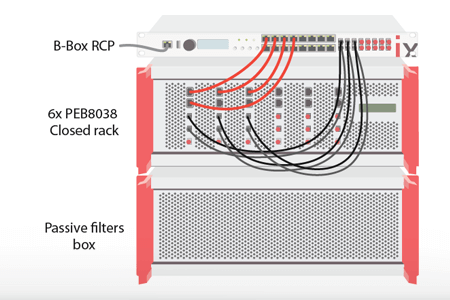

This page is a quick-start guide to build a 3 phase inverter using imperix equipment. It is specifically made to accompany users who want to…

The SFP output mailbox block allows sending data float (single) signals via the SFP optic cables. To recieve data float (single), the SFP input mailbox…

The SFP input mailbox block allows receiving float (single) signals via the SFP optic cables. To send data float (single), the SFP output mailbox block…

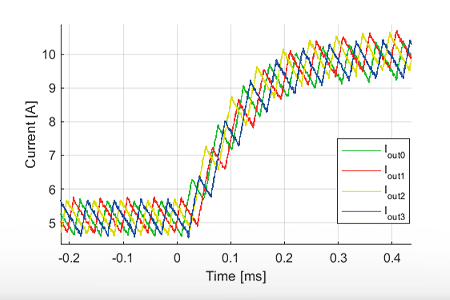

Introduction This technical note presents the implementation of an interleaved buck converter (multiphase step-down converter) and details an appropriate sampling method of the different currents…

The “dq0 to Alpha-Beta-Zero” converts a space vector from a rotating (dq0) to a stationary (αβ0) reference frame. The angle of the rotating reference frame…

The “Alpha-Beta-Zero to dq0” block converts a space vector from a stationary (αβ0) to a rotating reference frame (dq0). The angle of the rotating reference…

The “Alpha-Beta-Zero to abc” block computes a three-phase (abc) signal from a space vector in a stationary reference frame (αβ0). The transformation is performed using…

The “adc to Alpha-Beta-Zero” block computes the coordinates of a three-phase (abc) signal in a stationary reference frame (αβ0). The transformation is performed using the…

End of content

End of content