PP-PWM – Programmed Patterns PWM

The FPGA-based PP-PWM (programmed pulse pattern) peripheral provides a specialized PWM scheme for two and three-level inverters, which relies on pre-computed pulse patterns. This type…

The FPGA-based PP-PWM (programmed pulse pattern) peripheral provides a specialized PWM scheme for two and three-level inverters, which relies on pre-computed pulse patterns. This type…

This page covers a possible control algorithm for controlling the secondary DC voltage of a DAB converter. A working prototype is built using PEH full-bridge…

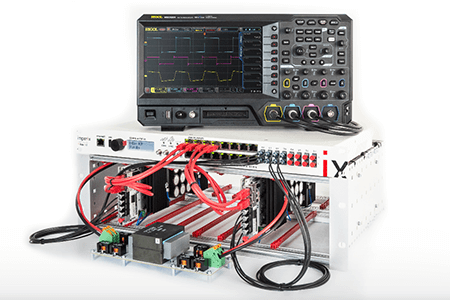

This page provides first-time users of the power electronics bundle with step-by-step guidance for implementing a simple application, which can also serve as a self-commissioning…

The brake (BRK) block provides access to the brake control unit of the Motor Interface for B-Box RCP. The Motor Interface for B-Box RCP features a brake…

The torque sensor (TRQ) block reads the voltage output of a torque sensor and converts it to torque. It targets drive applications. The B-Box RCP…

The temperature sensor (TMP) block provides access to the temperature measurement from a PT100 or PT1000 sensor for drive applications. The B-Box RCP supports up…

The sin/cos encoder (S/C) block retrieves the Sine and Cosine signals of a sin/cos encoder connected to the Motor Interface. The B-Box RCP supports up…

The hall sensor interface (HAL) block provides access to the commutation signals from Hall effect sensors of a brushless DC motor. The B-Box RCP supports…

The resolver interface block decodes the feedback from a resolver and provides the position of the rotor for drive applications. The B-Box RCP supports up…

The incremental encoder interface (INC) block decodes the A, B, Z signals from an incremental encoder for motor drive applications. The B-Box supports up to…

End of content

End of content