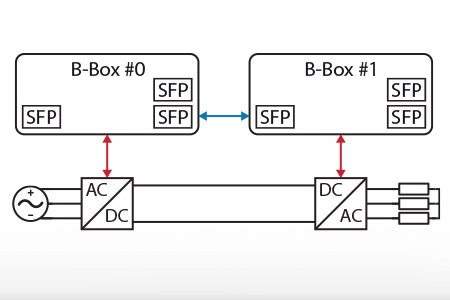

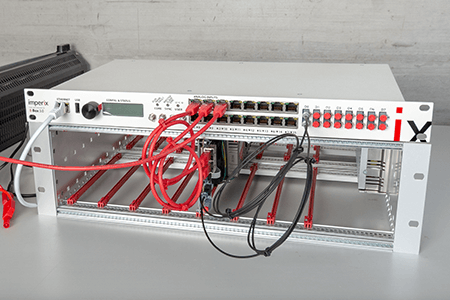

Coordinated control of a back-to-back inverter

This technical note gives general insights on the implementation of coordinated control using imperix’s rapid control prototyping solutions. A grid-tied back-to-back three-phase inverter is given…

This technical note gives general insights on the implementation of coordinated control using imperix’s rapid control prototyping solutions. A grid-tied back-to-back three-phase inverter is given…

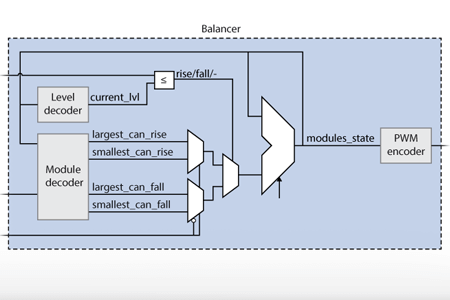

The SS-PWM peripheral provides a specialized Pulse Width Modulation scheme (PWM) for multilevel converters, which directly integrates means for balancing series-connected submodules. Such an approach…

This technical note offers insights into the SS-PWM peripheral block, which is part of the standard firmware of imperix controllers. The SS-PWM block provides multilevel…

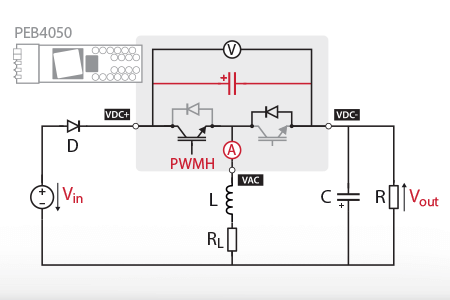

This technical note describes the operating principles of a buck-boost converter. A possible open-loop control implementation of this converter, targeting the B-Box RCP or B-Board PRO with both C/C++ and automated code…

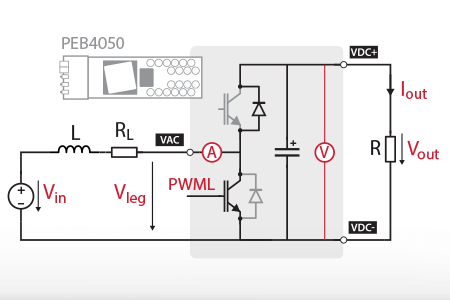

This technical note describes the operating principles of a step-up boost converter. A possible open-loop control implementation of this converter, targeting the B-Box RCP or B-Board PRO with both C/C++ and automated…

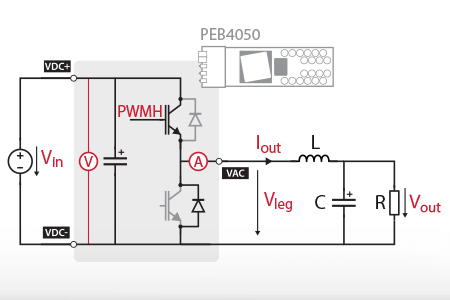

This technical note describes the operating principles of a step-down buck converter. A possible open-loop control implementation of this converter, targeting the B-Box RCP or B-Board PRO with both C/C++ and automated…

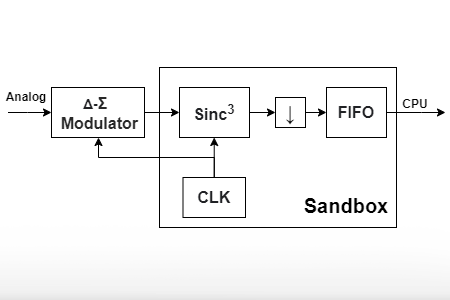

This technical note shows how to build a decoder IP for a Delta-Sigma Modulator and establish communication with such a device through USR ports of…

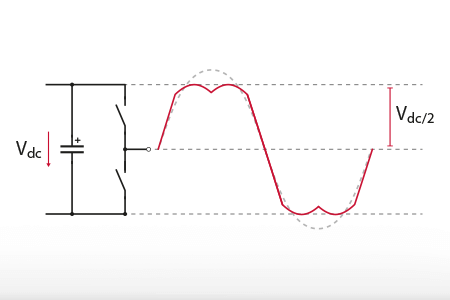

What is the difference between Space Vector (SVPWM) and Sinusoidal Pulse Width Modulation (SPWM)? This article presents the advantages of the SVPWM technique over SPWM…

This quick-start guide describes how to build a buck converter controlled in open-loop using power modules and the B-Box RCP 3.0 programmable controller using the…

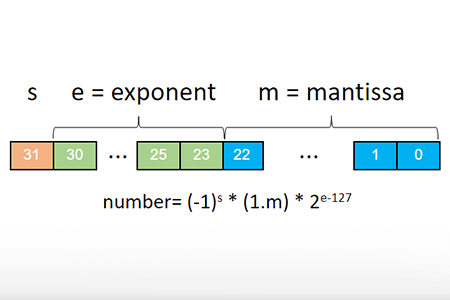

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

End of content

End of content