dq0 to abc

The “dq0 to abc” block computes a three-phase (abc) signal from a space vector in a rotating reference frame (dq0). The angle of the rotating…

The “dq0 to abc” block computes a three-phase (abc) signal from a space vector in a rotating reference frame (dq0). The angle of the rotating…

The “abc to dq0” block computes the coordinates of a three-phase (abc) signal in a rotating reference frame (dq0). The angle of the rotating reference…

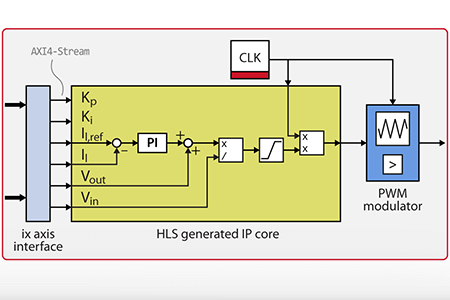

High-level synthesis (HLS) tools greatly facilitate the implementation of complex power electronics controller algorithms in FPGA. Indeed HLS tools allow the user to work at…

The Xilinx blockset for MATLAB & Simulink is a single toolbox that unifies Model Composer (HLS), System Generator for DSP (HDL) as well as the Xilinx AI…

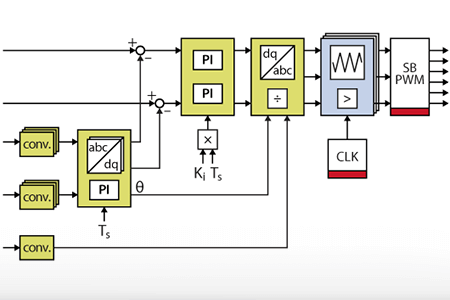

This note presents an FPGA control implementation of a grid-tied current-controlled inverter. It combines several control modules presented in different Technical Notes to form a…

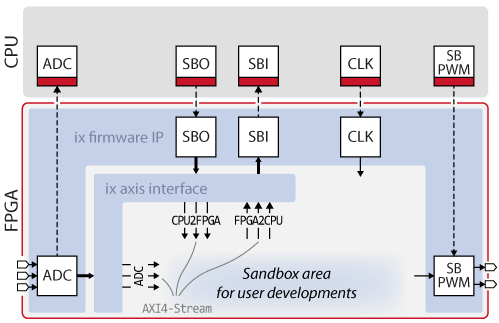

While the standard imperix workflow utilises the ACG SDK (for Simulink or PLECS ) or the CPP SDK (for C/C++) to program the controller’s CPU,…

Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the…

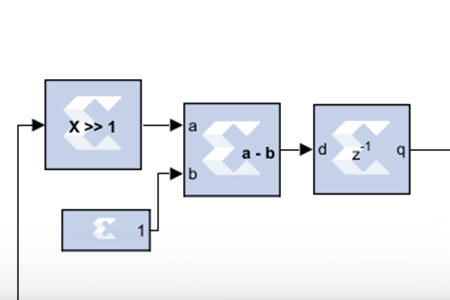

Xilinx System Generator for DSP (SysGen) is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical blocks programming. Users can…

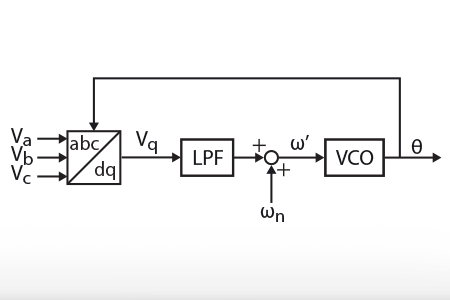

This note provides insights into the operating principle of a synchronous reference frame PLL (SRF PLL), also known as DQ-type PLL. An implementation of an…

The CAN_in block implements an input mailbox that supports receiving messages using the CAN bus protocol. To send messages, the CAN out block should be…

End of content

End of content