DEC – Angle decoder input

The angle decoder (DEC) block decodes quadrature-encoded signals produced by incremental encoders for motor drive applications. The imperix controllers provide decoder inputs for quadrature-encoder speed/position…

The angle decoder (DEC) block decodes quadrature-encoded signals produced by incremental encoders for motor drive applications. The imperix controllers provide decoder inputs for quadrature-encoder speed/position…

The GPO block, or its equivalent C++ routines, is responsible for asserting the specific logic states of the General Purpose Outputs (GPO) pins. This interface…

The GPI block (or its C++ routines) is responsible for reading the the logic states of the General Purpose Inputs (GPI) pins. This function allows…

The DAC block, or its equivalent C++ routines, is used to apply a given value to one of the Digital-to-Analog Converter (DAC) channels of the…

The ADC block (or C++ routines) are used to access data from a given Analog-to-Digital Converter (ADC) channel. They also serve to configure how this…

Imperix controllers feature 4 clock generators, CLK0, CLK1, CLK2 and CLK3, running at 250 MHz. They provide time bases for FPGA resources such as the…

The CONFIG block primarily serves to configure the main clock (CLK0) as well as its derivatives. Together, these clocks define the frequency and phase of…

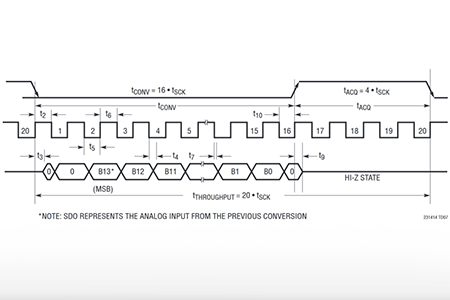

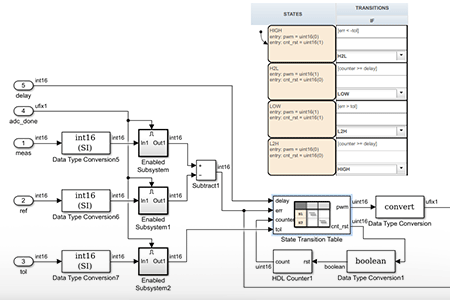

This technical note shows how an SPI communication link can be established between an FPGA and an external Analog-to-Digital Converter (ADC). The development setup will…

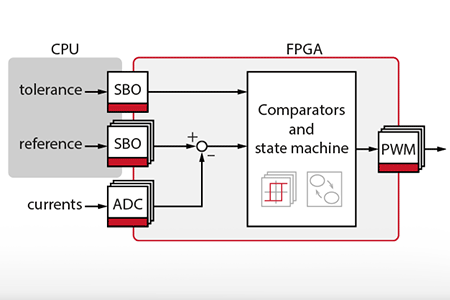

This technical note shows how the implementation of an FPGA-based hysteresis controller can be conducted, starting from the modeling stage, following with automated VHDL code…

This technical note provides an example of how a fast hysteresis current controller can be implemented, leveraging the possibility of editing the FPGA firmware for…

End of content

End of content