Xilinx System Generator introduction

Xilinx System Generator for DSP (SysGen) is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical blocks programming. Users can…

Xilinx System Generator for DSP (SysGen) is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical blocks programming. Users can…

Model Composer is a Simulink add-on software developed by Xilinx. It is a high-level synthesis (HLS) tool that allows the user to program an FPGA-based…

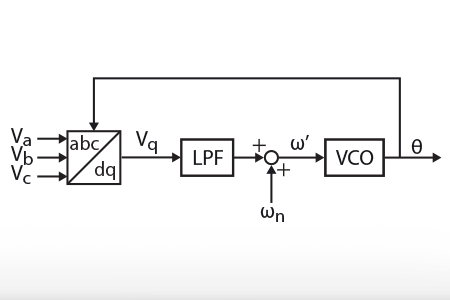

This note provides insights into the operating principle of a synchronous reference frame PLL (SRF PLL), also known as DQ-type PLL. An implementation of an…

The CAN_in block implements an input mailbox that supports receiving messages using the CAN bus protocol. To send messages, the CAN out block should be…

The tunable parameter block creates a variable that can be altered in real-time using imperix Cockpit. It supports the int32, uint32, and float data types. Simultaneously, the tunable parameter…

The probe variable block creates a variable that can be watched and logged in real-time using using imperix Cockpit. It supports the int32, uint32, and…

The Core state block returns the state of the target: The block also provides a second signal called “reset” that can be wired to the…

The external reset block provides a signal that can be wired to the external reset input of PID controllers to keep the integrator at reset…

This block issues a request to enable or disable the PWM outputs, similar to the “Enable outputs” button of BB Control utility software. It issues…

The Sandbox Output towards FPGA (SBO) block writes the value of the SBO registers in the FPGA. It is used to transfer data from the…

End of content

End of content