abc to dq0

The “abc to dq0” block computes the coordinates of a three-phase (abc) signal in a rotating reference frame (dq0). The angle of the rotating reference…

The “abc to dq0” block computes the coordinates of a three-phase (abc) signal in a rotating reference frame (dq0). The angle of the rotating reference…

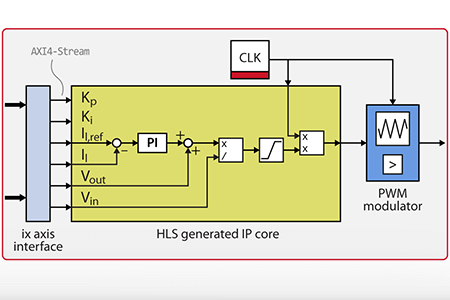

High-level synthesis (HLS) tools greatly facilitate the implementation of complex power electronics controller algorithms in FPGA. Indeed HLS tools allow the user to work at…

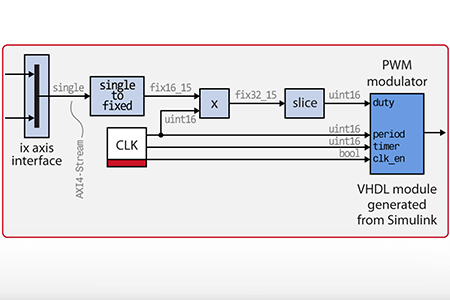

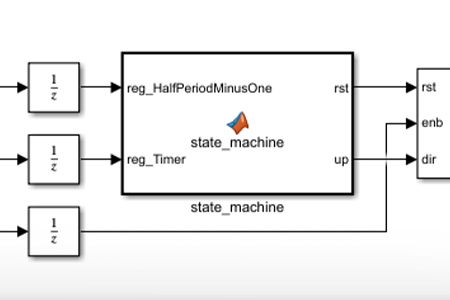

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents…

The Xilinx blockset for MATLAB & Simulink is a single toolbox that unifies Model Composer (HLS), System Generator for DSP (HDL) as well as the Xilinx AI…

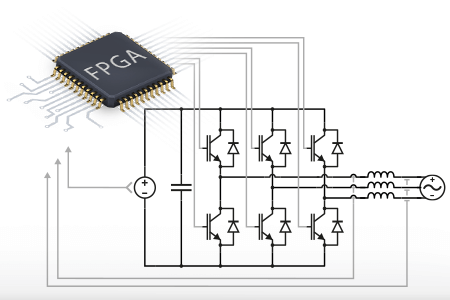

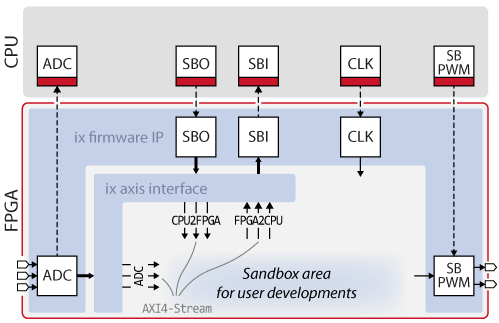

Usually, the user programs the imperix controller’s CPU using imperix ACG SDK or C++ SDK, and uses the pre-implemented FPGA peripherals such as the ADC…

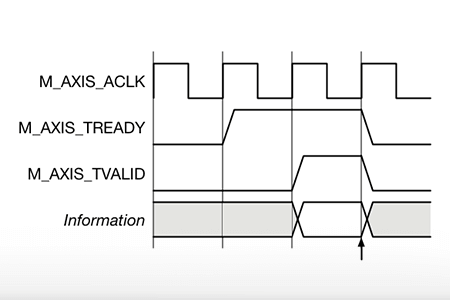

This page presents some useful Xilinx IP cores for Vivado. These IPs use the widely used AXI4-Stream protocol to easily exchange data with other Xilinx…

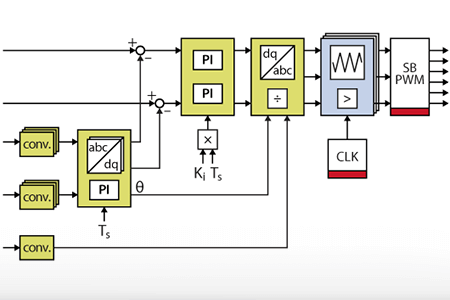

This note presents an FPGA control implementation of a grid-tied current-controlled inverter. It combines several control modules presented in different Technical Notes to form a…

While the standard imperix workflow utilises the ACG SDK (for Simulink or PLECS ) or the CPP SDK (for C/C++) to program the controller’s CPU,…

HDL Coder is a MATLAB add-on that can generate VHDL and Verilog code from MATLAB functions or Simulink models. This approach can greatly accelerate rapid…

Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the…

End of content

End of content