How to build a buck converter

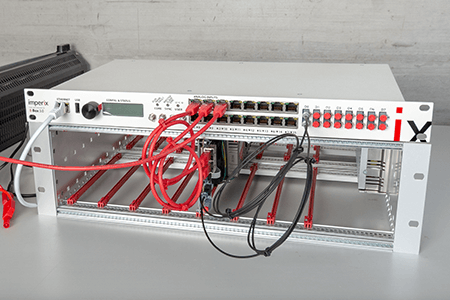

This quick-start guide describes how to build a buck converter controlled in open-loop using power modules and the B-Box RCP 3.0 programmable controller using the…

This quick-start guide describes how to build a buck converter controlled in open-loop using power modules and the B-Box RCP 3.0 programmable controller using the…

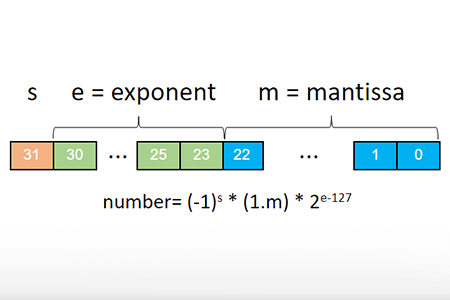

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

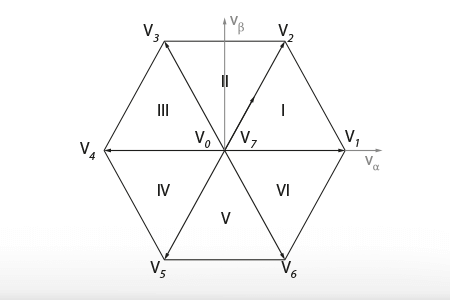

What is the space vector modulation (SVM) technique and how does it work? To answer these questions, this article introduces first the notions of active…

This page is a quick-start guide to build a 3 phase inverter using imperix equipment. It is specifically made to accompany users who want to…

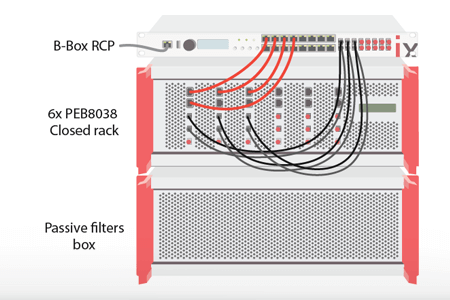

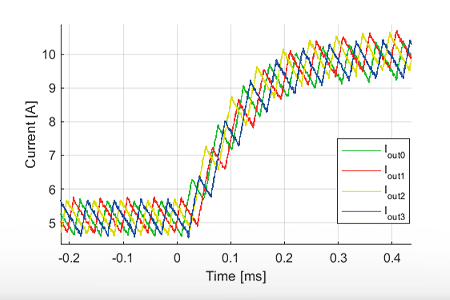

Introduction This technical note presents the implementation of an interleaved buck converter (multiphase step-down converter) and details an appropriate sampling method of the different currents…

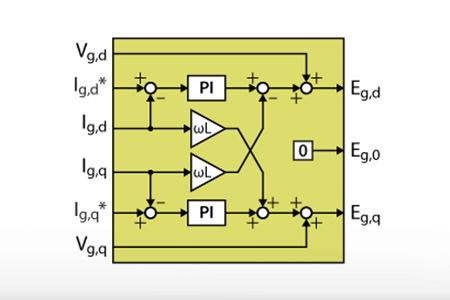

Control algorithms for power electronics converters often rely on PI controllers executed on the CPU of the controller. That’s the technique used in most of…

The “dq0 to Alpha-Beta-Zero” converts a space vector from a rotating (dq0) to a stationary (αβ0) reference frame. The angle of the rotating reference frame…

The “Alpha-Beta-Zero to dq0” block converts a space vector from a stationary (αβ0) to a rotating reference frame (dq0). The angle of the rotating reference…

The “Alpha-Beta-Zero to abc” block computes a three-phase (abc) signal from a space vector in a stationary reference frame (αβ0). The transformation is performed using…

End of content

End of content