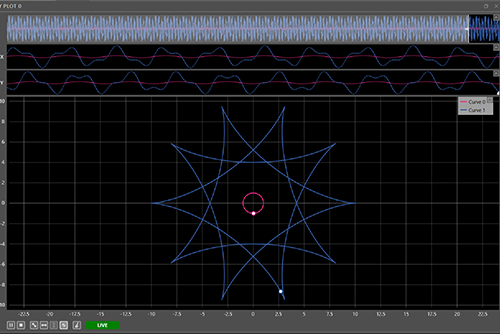

XY Plot Module

This article describes how to use the XY plot module of imperix Cockpit to interact with the user code running on imperix controllers, namely the…

This article describes how to use the XY plot module of imperix Cockpit to interact with the user code running on imperix controllers, namely the…

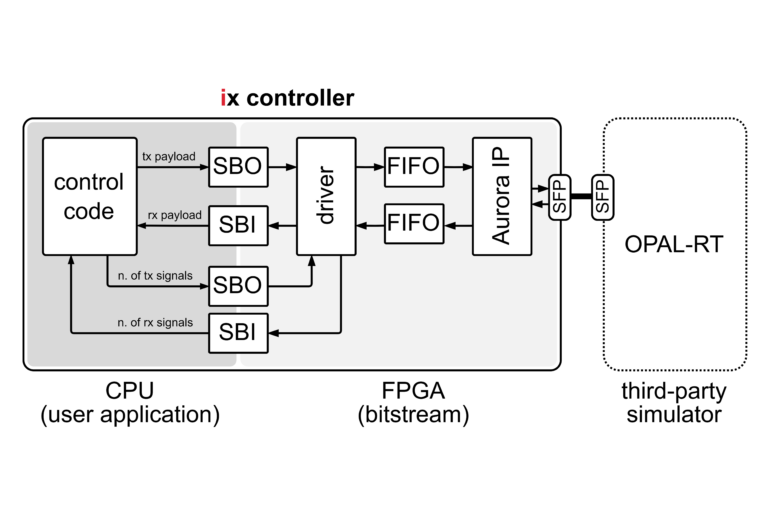

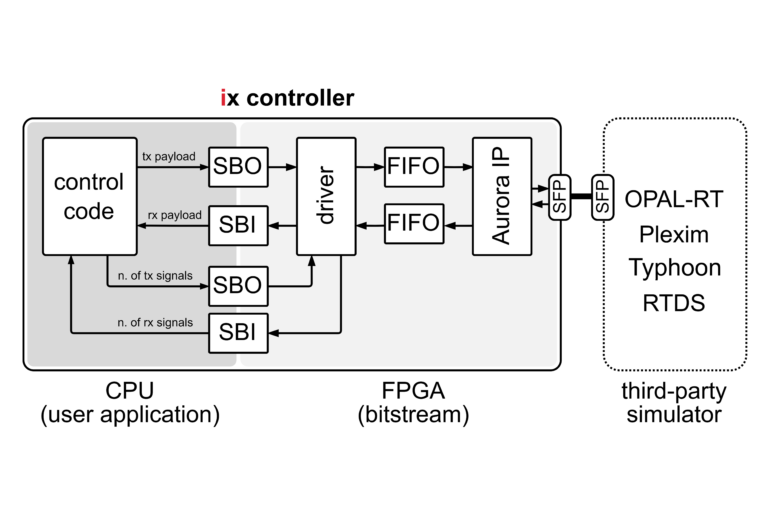

This page presents a practical example of Aurora communication with OPAL-RT simulators, specifically the OP4510 and OP4512. It provides a ready-to-use user application, along with…

While imperix controllers are typically programmed with applications built in Simulink or PLECS, imperix also provides direct access to FPGA resources through its FPGA development…

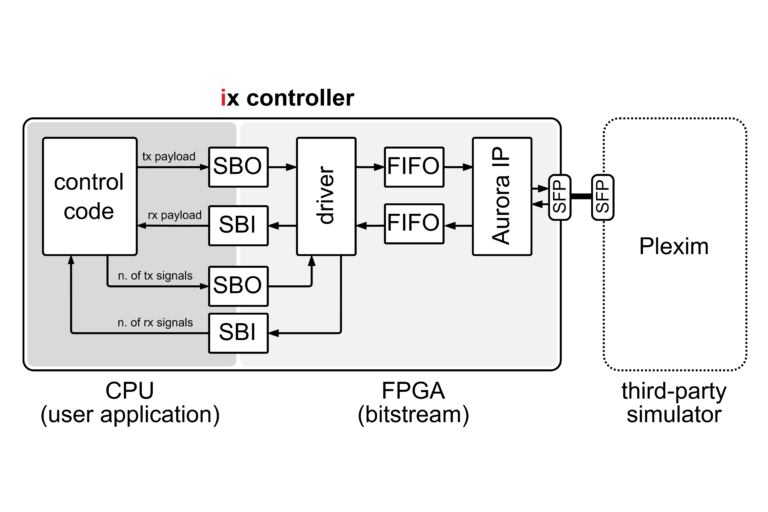

This page presents a practical example of Aurora communication with Plexim simulators, namely the RT-Box 1, RT-Box 2 and RT-Box 3. It provides a ready-to-use…

The EnDat block instantiates an EnDat master to communicate with compatible digital encoders and similar digital sensors, typically in motor drive applications. This block is…

The BiSS-C block instantiates a Bidirectional Synchronous Serial – Communication (BiSS-C) master to communicate with BiSS-C-compatible digital encoders and similar digital sensors, typically in motor…

The SSI block instantiates a Synchronous Serial Interface (SSI) master to communicate with SSI-compatible digital encoders and similar digital sensors, typically in motor drive applications….

Debugging an FPGA design can be difficult without clear visibility into the high-speed logic fabric, where signals change at nanosecond scales. Xilinx Integrated Logic Analyzer…

Introduction Power electronic converters pose a specific sampling challenge: the signals of interest (currents and voltages) are low-frequency components, but they are combined with a…

This page is a quick-start guide to build an interleaved boost converter using imperix equipment. It is specifically made to accompany users who want to…

End of content

End of content