ADC – Analog data acquisition

The ADC block (or C++ routines) are used to access data from a given Analog-to-Digital Converter (ADC) channel. They also serve to configure how this…

The ADC block (or C++ routines) are used to access data from a given Analog-to-Digital Converter (ADC) channel. They also serve to configure how this…

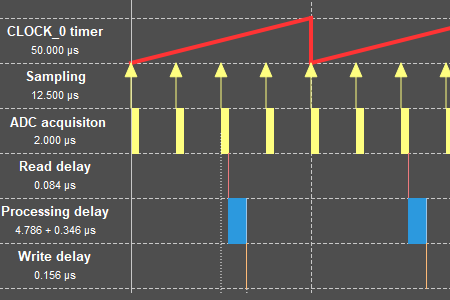

Imperix controllers feature 4 clock generators, CLK0, CLK1, CLK2 and CLK3, running at 250 MHz. They provide time bases for FPGA resources such as the…

The CONFIG block primarily serves to configure the main clock (CLK0) as well as its derivatives. Together, these clocks define the frequency and phase of…

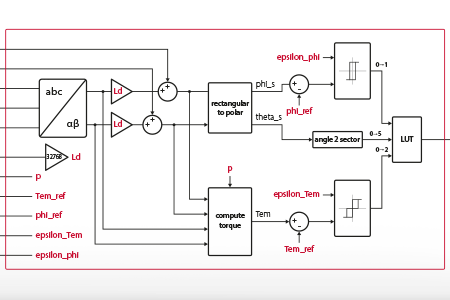

This technical note presents an FPGA-based Direct Torque Control (DTC) of a PMSM motor using Vivado HLS, coupled with the possibility to customize the FPGA…

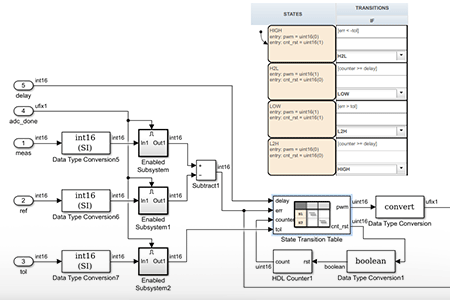

This technical note shows how the implementation of an FPGA-based hysteresis controller can be conducted, starting from the modeling stage, following with automated VHDL code…

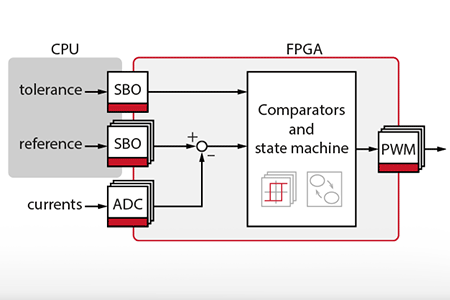

This technical note provides an example of how a fast hysteresis current controller can be implemented, leveraging the possibility of editing the FPGA firmware for…

This application showcases a multi-converter system consisting of three DC/AC converters connected to a microgrid, representing a typical scenario such as three photovoltaic inverters sharing…

This example generates three phase alternating currents from a voltage source inverter in an open loop manner. It can be used in a grid-forming application.

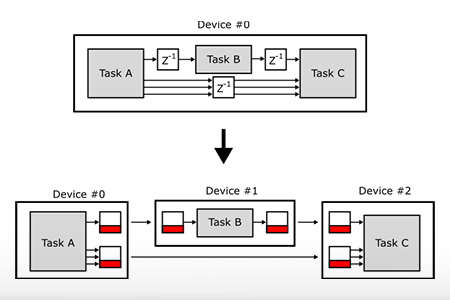

This note focuses on the multi-master feature which allows executing control codes on multiple imperix power converter controllers interconnected using optical fiber (SFP). The imperix in-house…

In a standard configuration, the control algorithm executes immediately following each sampling event. The SCLK multiplier modifies this behavior by allowing multiple sampling events to…

End of content

End of content