TPI SB-PWM – Helper block

The TPI SB-PWM helper block is a wrapper that simplifies the use of the SB-PWM block with the all-in-one programmable inverter (TPI8032 22kW). The TPI…

The TPI SB-PWM helper block is a wrapper that simplifies the use of the SB-PWM block with the all-in-one programmable inverter (TPI8032 22kW). The TPI…

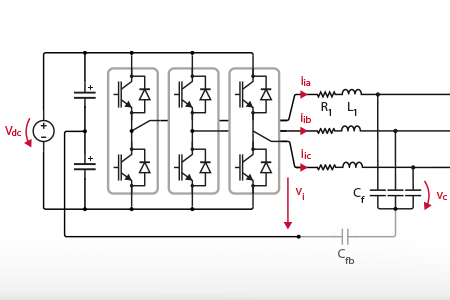

This article introduces an example of Finite Control Set Model Predictive Control (FCS-MPC) for an LCL-filtered voltage-controlled inverter. The proposed control implementation is derived from…

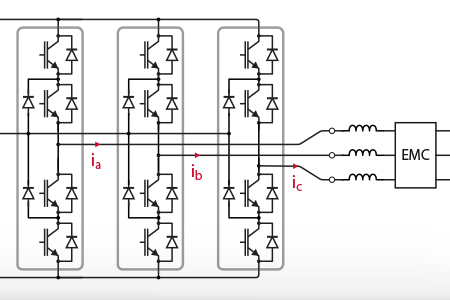

Closed-loop current control for a grid-tied Neutral Point Clamped (NPC) inverter. The considered setup is a three-phase three-wire NPC inverter supplied by a DC source and connected to the grid.

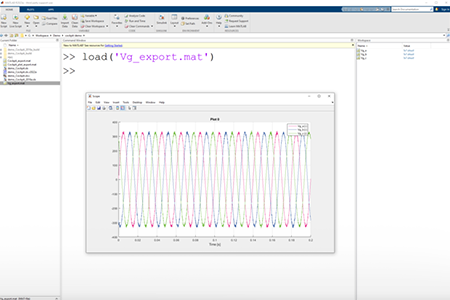

As described in the Cockpit user guide, imperix Cockpit provides the user with the option to export monitored signals in different forms. This article provides…

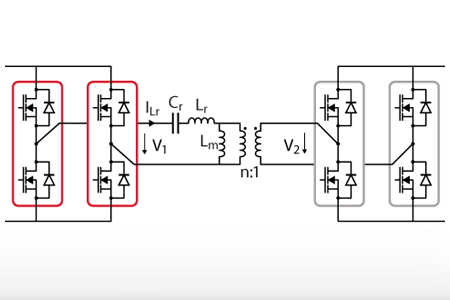

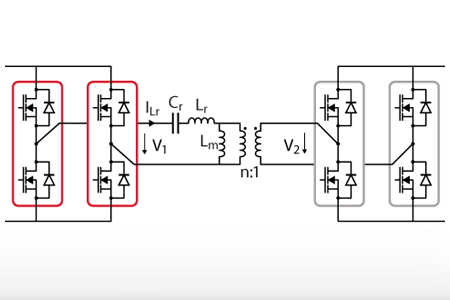

Thanks to its flexible output voltage range, the LLC resonant converter is a popular choice of topology for battery charger applications, such as onboard chargers…

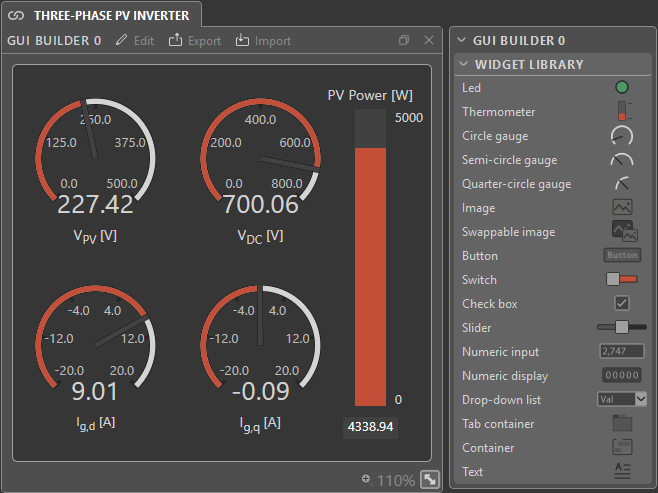

This user guide explains how to use the GUI Builder module of imperix Cockpit to interact with imperix power converter controllers, namely the B-Box 4,…

This technical note provides an introduction to the LLC converter, which is an isolated DC-DC converter, popular in a multitude of fields.

The fundamental harmonic approximation is presented as a modeling technique before the operation of the LLC converter is discussed above resonance, at resonance, and below resonance.

Following that, this technical note demonstrates how to build and operate an LLC converter using imperix hardware and software, and compares the physical implementation with the theory and the simulated plant.

The ACG SDK blocksets for Simulink and PLECS contain blocks specific to the all-in-one programmable inverter (TPI8032 22kW). These wrappers simplify the use of usual blocks,…

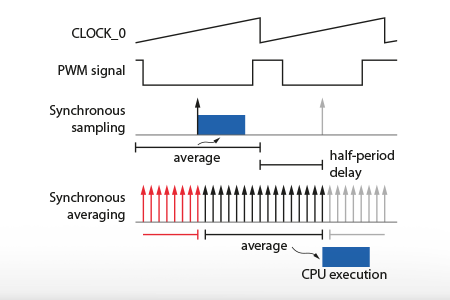

Synchronous averaging is a measurement processing method that computes the average value of an analog signal over one full switching period. In contrast, synchronous sampling…

The TPI SV-PWM helper block is a wrapper that simplifies the use of the SV-PWM block with the all-in-one programmable inverter (TPI8032 22kW). Since the…

End of content

End of content