How to build a variable speed drive

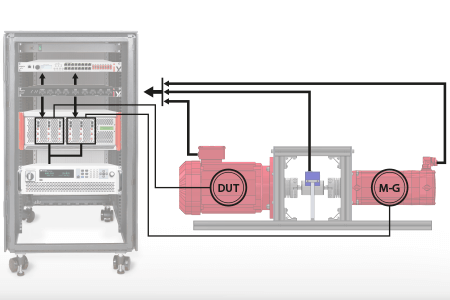

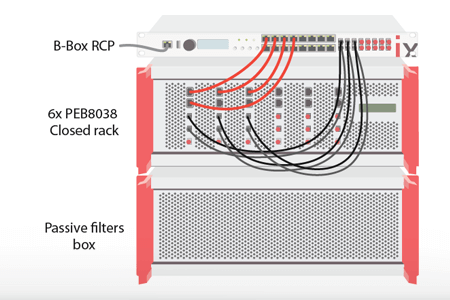

This page gives an overview of possible variable speed drive (VSD) configurations and how to implement them using imperix solutions. Thanks to a modular approach,…

These notes are specifically related to imperix products. They address both control or power hardware, as well as software solutions. Their aim is to document what users should understand to properly use imperix products. Product notes, therefore, provide complementary information with respect notably to product datasheets.

This page gives an overview of possible variable speed drive (VSD) configurations and how to implement them using imperix solutions. Thanks to a modular approach,…

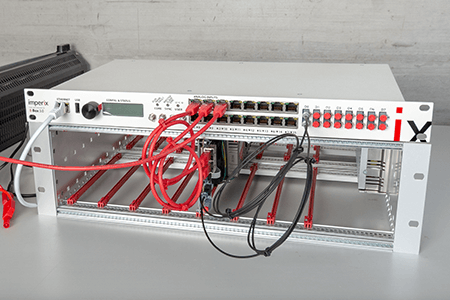

This quick-start guide describes how to build a buck converter controlled in open-loop using power modules and the B-Box RCP 3.0 programmable controller using the…

This page provides step-by-step guidance to install Xilinx Vivado Design Suite, the tools used to program the FPGA of imperix controllers.

This page is a quick-start guide to build a 3 phase inverter using imperix equipment. It is specifically made to accompany users who want to…

The Xilinx blockset for MATLAB & Simulink is a single toolbox that unifies Model Composer (HLS), System Generator for DSP (HDL) as well as the Xilinx AI…

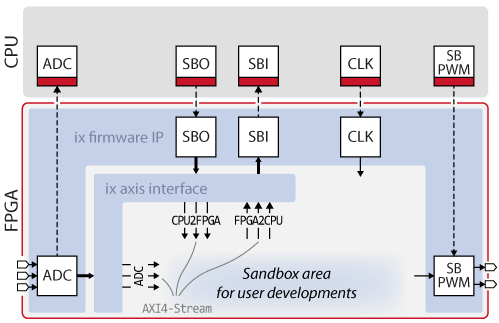

Usually, the user programs the imperix controller’s CPU using imperix ACG SDK or C++ SDK, and uses the pre-implemented FPGA peripherals such as the ADC…

While the standard imperix workflow utilises the ACG SDK (for Simulink or PLECS ) or the CPP SDK (for C/C++) to program the controller’s CPU,…

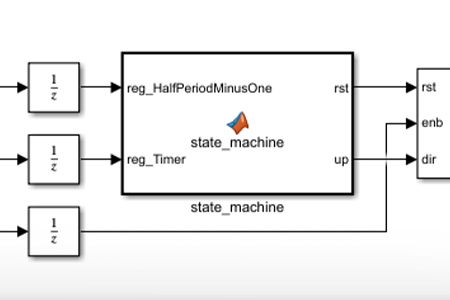

HDL Coder is a MATLAB add-on that can generate VHDL and Verilog code from MATLAB functions or Simulink models. This approach can greatly accelerate rapid…

Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the…

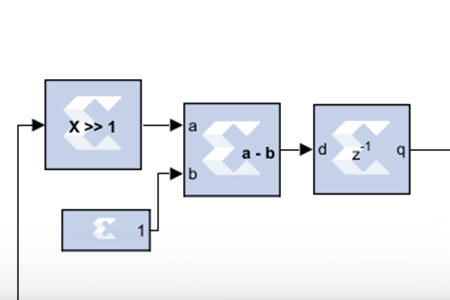

Xilinx System Generator for DSP (SysGen) is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical blocks programming. Users can…

End of content

End of content