Thermal simulation with Imperix Power library

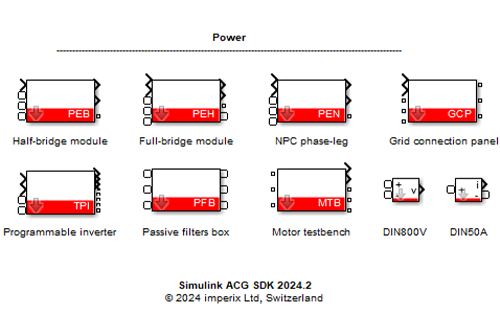

The imperix Power library is a blockset contained within the imperix ACG SDK that provides rapid and accurate modeling of imperix power products. Starting from 2025.1 BETA,…

These notes are specifically related to imperix products. They address both control or power hardware, as well as software solutions. Their aim is to document what users should understand to properly use imperix products. Product notes, therefore, provide complementary information with respect notably to product datasheets.

The imperix Power library is a blockset contained within the imperix ACG SDK that provides rapid and accurate modeling of imperix power products. Starting from 2025.1 BETA,…

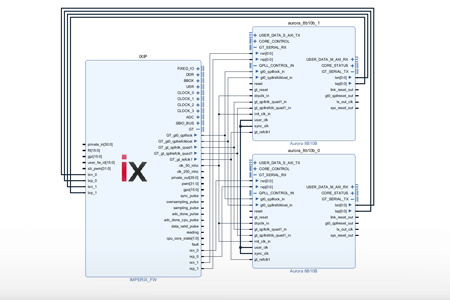

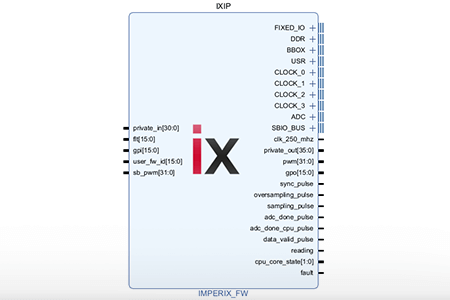

The SFP ports on imperix controllers are typically used for interconnecting devices in a RealSync network. However, when customizing the FPGA firmware, imperix designed the…

This page provides the imperix sources files required to start programming the FPGA on imperix controllers. The provided archive contains the imperix firmware IP and…

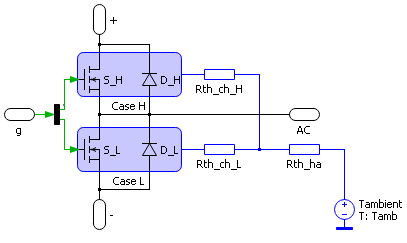

The imperix Power library is a blockset contained within the imperix ACG SDK, which contains accurate models of imperix power products. This article summarizes the…

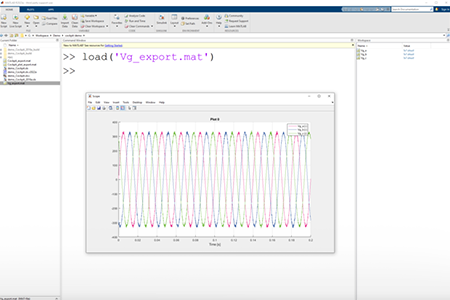

As described in the Cockpit user guide, imperix Cockpit provides the user with the option to export monitored signals in different forms. This article provides…

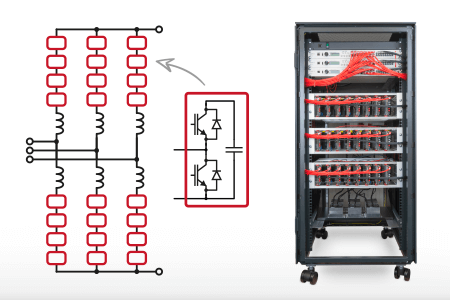

This article gives step-by-step instructions on how to operate the modular multilevel converter (MMC) bundle with a simple control algorithm.

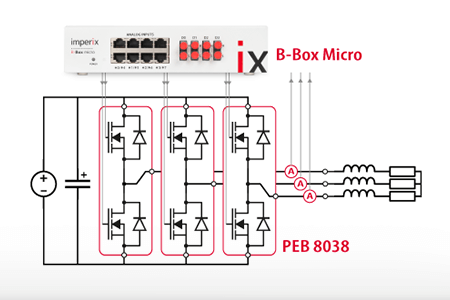

This article provides getting-started information for working with the B-Box Micro inverter controller , focusing on the programming workflow and highlighting the easy transition from…

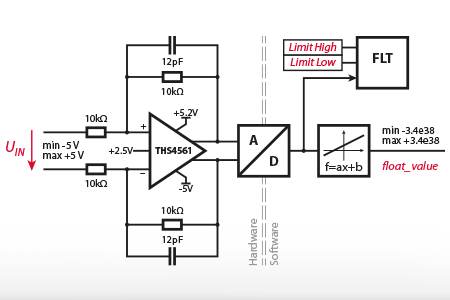

This page covers the configuration of the analog inputs of the B-Box Micro. The B-Box Micro possesses 8 analog inputs with identical channels. The equivalent…

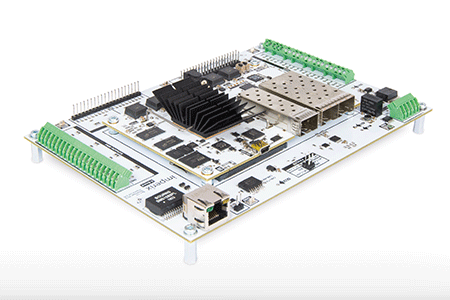

This document is primarily intended for electronic board designers wishing to integrate the B-Board PRO into their designs. It essentially serves as documentation for the Eval-Board marketed…

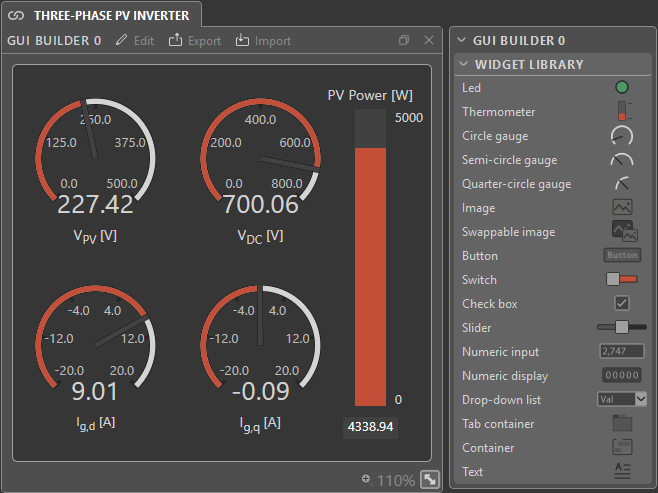

This user guide explains how to use the GUI Builder module of imperix Cockpit to interact with imperix power converter controllers, namely the B-Box 4,…

End of content

End of content