INC – Incremental encoder input

The incremental encoder interface (INC) block decodes the A, B, Z signals from an incremental encoder for motor drive applications. The B-Box supports up to…

The incremental encoder interface (INC) block decodes the A, B, Z signals from an incremental encoder for motor drive applications. The B-Box supports up to…

The SS-PWM peripheral provides a specialized Pulse Width Modulation scheme (PWM) for multilevel converters, which directly integrates means for balancing series-connected submodules. Such an approach…

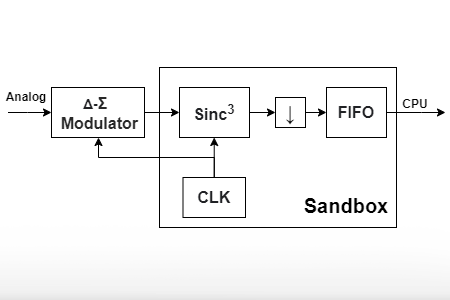

This technical note shows how to build a decoder IP for a Delta-Sigma Modulator and establish communication with such a device through USR ports of…

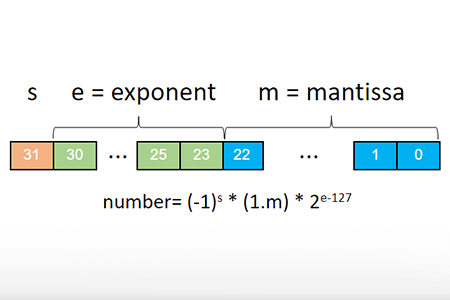

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

The SFP output mailbox block allows sending data float (single) signals via the SFP optic cables. To recieve data float (single), the SFP input mailbox…

The SFP input mailbox block allows receiving float (single) signals via the SFP optic cables. To send data float (single), the SFP output mailbox block…

The “dq0 to Alpha-Beta-Zero” converts a space vector from a rotating (dq0) to a stationary (αβ0) reference frame. The angle of the rotating reference frame…

The “Alpha-Beta-Zero to dq0” block converts a space vector from a stationary (αβ0) to a rotating reference frame (dq0). The angle of the rotating reference…

The “Alpha-Beta-Zero to abc” block computes a three-phase (abc) signal from a space vector in a stationary reference frame (αβ0). The transformation is performed using…

The “adc to Alpha-Beta-Zero” block computes the coordinates of a three-phase (abc) signal in a stationary reference frame (αβ0). The transformation is performed using the…

End of content

End of content