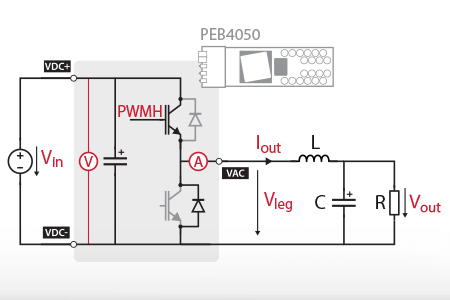

Step-down buck converter

This technical note describes the operating principles of a step-down buck converter. A possible open-loop control implementation of this converter, targeting the B-Box RCP or B-Board PRO with both C/C++ and automated…

These notes present solutions for the implementation of control software, with practical, imperix-related aspects in mind. They mostly focus on one specific subsystem and may link to other technical notes if needed. Technical notes are application-independent.

This technical note describes the operating principles of a step-down buck converter. A possible open-loop control implementation of this converter, targeting the B-Box RCP or B-Board PRO with both C/C++ and automated…

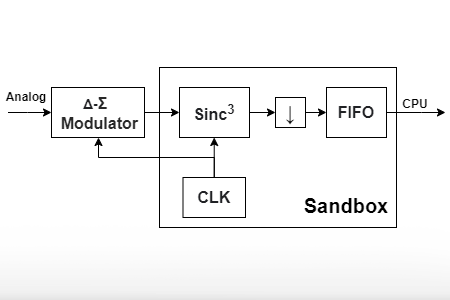

This technical note shows how to build a decoder IP for a Delta-Sigma Modulator and establish communication with such a device through USR ports of…

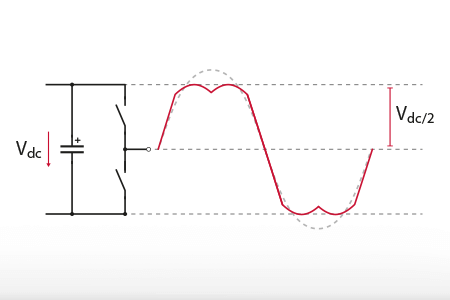

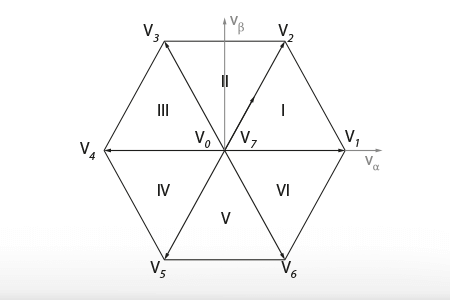

What is the difference between Space Vector (SVPWM) and Sinusoidal Pulse Width Modulation (SPWM)? This article presents the advantages of the SVPWM technique over SPWM…

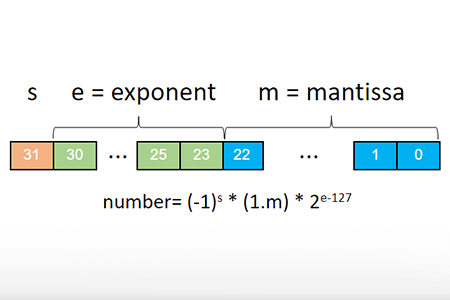

The choice of fixed vs floating-point arithmetic for an FPGA algorithm is a decision that has a significant impact on the FPGA resources usage, computation…

What is the space vector modulation (SVM) technique and how does it work? To answer these questions, this article introduces first the notions of active…

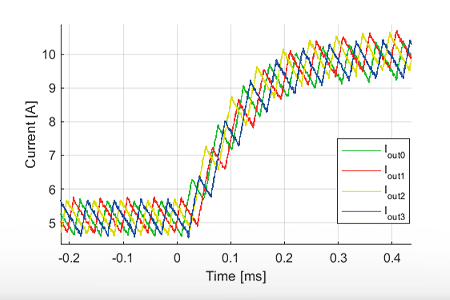

Introduction This technical note presents the implementation of an interleaved buck converter (multiphase step-down converter) and details an appropriate sampling method of the different currents…

Control algorithms for power electronics converters often rely on PI controllers executed on the CPU of the controller. That’s the technique used in most of…

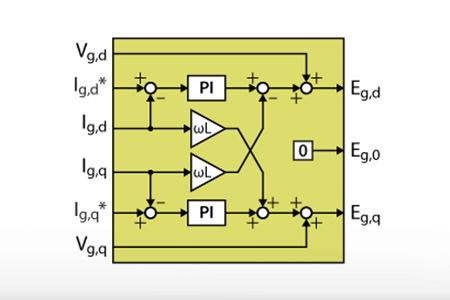

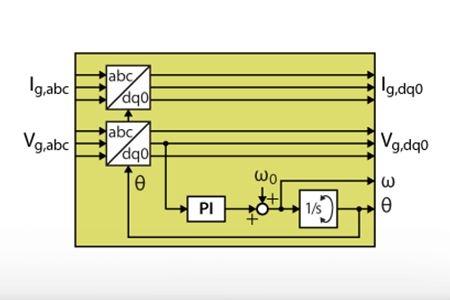

The operation of a grid-tied power converter (such as the 3-phases PV inverter) requires that the control software implements a grid synchronization technique. One well-known…

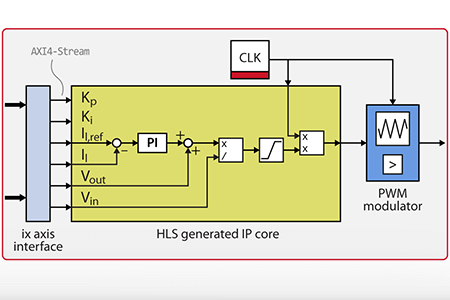

High-level synthesis (HLS) tools greatly facilitate the implementation of complex power electronics controller algorithms in FPGA. Indeed HLS tools allow the user to work at…

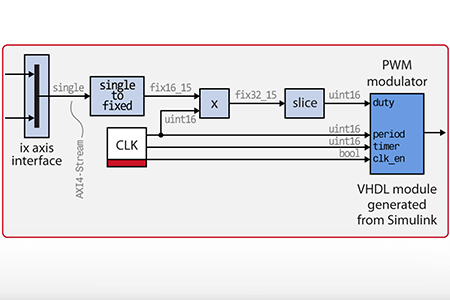

To implement power converter control algorithms in an FPGA, it is often required to develop an FPGA-based pulse-width modulation (PWM) module. Therefore, this note presents…

End of content

End of content