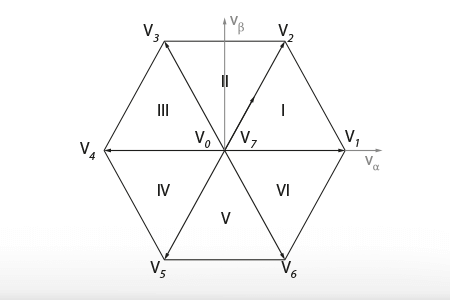

Space Vector Modulation (SVM)

What is the space vector modulation (SVM) technique and how does it work? To answer these questions, this article introduces first the notions of active…

What is the space vector modulation (SVM) technique and how does it work? To answer these questions, this article introduces first the notions of active…

The SFP output mailbox block allows sending data float (single) signals via the SFP optic cables. To recieve data float (single), the SFP input mailbox…

The SFP input mailbox block allows receiving float (single) signals via the SFP optic cables. To send data float (single), the SFP output mailbox block…

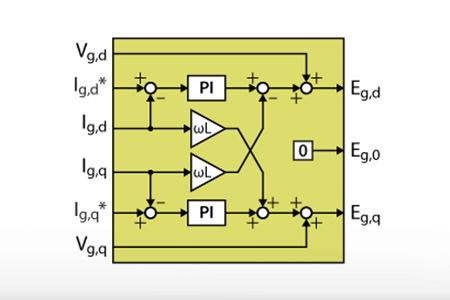

Control algorithms for power electronics converters often rely on PI controllers executed on the CPU of the controller. That’s the technique used in most of…

The “dq0 to Alpha-Beta-Zero” converts a space vector from a rotating (dq0) to a stationary (αβ0) reference frame. The angle of the rotating reference frame…

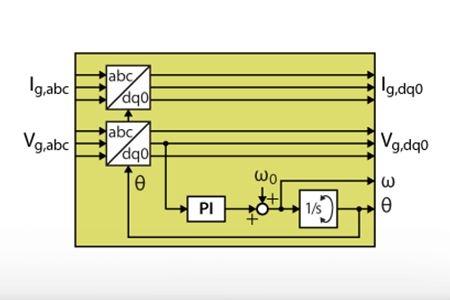

The “Alpha-Beta-Zero to dq0” block converts a space vector from a stationary (αβ0) to a rotating reference frame (dq0). The angle of the rotating reference…

The “Alpha-Beta-Zero to abc” block computes a three-phase (abc) signal from a space vector in a stationary reference frame (αβ0). The transformation is performed using…

The “adc to Alpha-Beta-Zero” block computes the coordinates of a three-phase (abc) signal in a stationary reference frame (αβ0). The transformation is performed using the…

The “dq0 to abc” block computes a three-phase (abc) signal from a space vector in a rotating reference frame (dq0). The angle of the rotating…

The operation of a grid-tied power converter (such as the 3-phases PV inverter) requires that the control software implements a grid synchronization technique. One well-known…

End of content

End of content